组合逻辑概述

由MOS获得基本逻辑门之后,再由门级电路形成组合逻辑电路。组合逻辑电路有三种表示方法:

(a)真值表

(b)结构化(即门级)原理图

(c)布尔方程

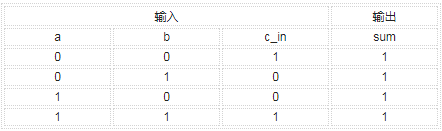

示例:例如一个单bit全加器,实现的是两个输入信号 a,b以及进位位 c_in的相加。输出一个相加的结果sum和一个进位位c_out。

其真值表如下:

根据真值表可以直接写出其布尔方程式。

获得某个输出的积之和(多项做与然后再做或)的布尔表达式方法如下:

1. 找到输出为1的对应的输入,如果此输入为0则取反。将输入做与。

2. 将上面所有的与项再做或操作。

以上面的全加器为例。使得输出sum为1的有:

故对应sum的积之和布尔表达式如下(*表示与操作,+表示或操作, ' 表示取反):

sum = a' * b' * c_in+a' * b * c_in'+a * b' * c_in' + a * b * c_in

同样分析可以得出 c_out的积之和布尔表达式如下:

c_out = a' * b * c_in+a * b' * c_in+a * b * c_in' + a * b * c_in

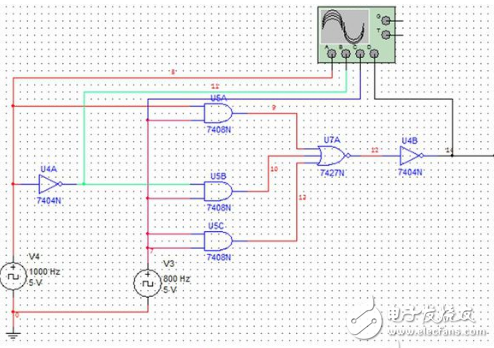

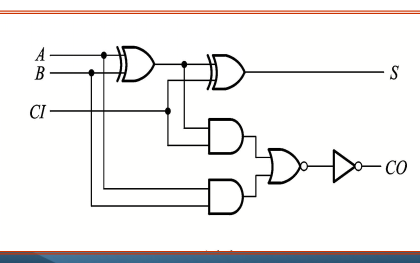

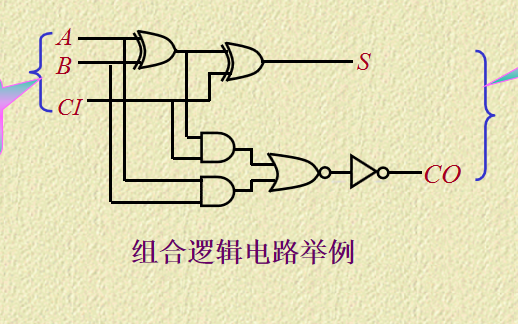

根据积之和表达式就可以得出相应的积之和对应的门级电路。以与或门构成。下面是sum的积之和电路,这里由三个2输入或门实现一个四输入或门逻辑。

相应的c_out的积之和门级电路如下。

可以看到这样获得积之和布尔表达式与对应的电路都是两级的,前面一级为与门逻辑,后面一级为或门逻辑。

当然不止只有积之和这一种表达方式,还可以利用狄摩根定律去转化成和之积的表达方式。

狄摩根定律如下( " ' " 表示取反," * " 表示与, " + "表示或):

(a + b + c + ...) ' = a' * b' * c' * ...

(a * b * c * ...) ' =a' + b' + c' + ...

根据狄摩根定律第二条,就可以将积之和布尔表达式转化成和之积形式;根据狄摩根定律第一条,就可以将和之积布尔表达式转化成积之和形式。

这里以将sum的积之和布尔表达式转化成和之积形式为例。

sum = ( (a' * b' * c_in+a' * b * c_in'+a * b' * c_in' + a * b * c_in)' )'

= ( (a' * b' * c_in)' * (a' * b * c_in')' * (a * b' * c_in')' * (a * b * c_in)') '

= ( ( a+b+c_in' )*( a+b'+c_in )*( a'+b+c_in )*(a' + b' + c_in') )'

从布尔表达式可以看到,和之积表达式的的前级为或门逻辑,后一级为与门逻辑。

Verilog对组合逻辑电路的描述,可以分为结构级描述,数据流级描述,行为级描述三种方式。

以上面对sum这个电路描述为例,将sum这个电路作为一个完整的module描述,给这个电路取个名字为get_sum。

结构级描述方式如下(其中not是表示非门,and表示与门,or表示或门):

module get_sum(

input a,

input b,

input c_in,

output sum

);

wire a_n,b_n,c_in_n;

not (a_n,a);

not (b_n,b);

not (c_in_n,c_in);

wire and_o1,and_o2,and_o3,and_o4;

and (and_o1,a_n,b_n,c_in) ;

and (and_o2,a_n,b,c_in_n) ;

and (and_o3,a,b_n,c_in_n) ;

and (and_o4,a,b,c_in) ;

wire or_o1,or_o2;

or (or_o1,and_o1,and_o2);

or (or_o2,and_o3,and_o4);

or (sum,or_o1,or_o2);

endmodule

数据流级描述方式(& 与,| 或 ,~ 非):

module get_sum(

input a,

input b,

input c_in,

output sum

);

wire a_n,b_n,c_in_n;

assign a_n = ~a;

assign b_n = ~b;

assign c_in_n = ~c_in;

wire and_o1,and_o2,and_o3,and_o4;

assign and_o1 = a_n&b_n&c_in;

assign and_o2 = a_n&b&c_in_n;

assign and_o3 = a&b_n&c_in_n;

assign and_o4 = a&b&c_in;

wire or_o1,or_o2;

assign or_o1 = and_o1 | and_o2;

assign or_o2 = and_o3 | and_o4;

assign sum = or_o1 | or_o2;

endmodule

行为级描述方式(这里采用了case语句,也可以采用if else语句;{ }是位拼接符,如{a,b,c_in}就是将a,b,c_in拼成一个三位的数据,a为最高位,b为次高位,c_in为最低位):

module get_sum(

input a,

input b,

input c_in,

output reg sum

);

always @( * ) begin

case( {a,b,c_in} )

3'b001: sum = 1'b1;

3'b010: sum = 1'b1;

3'b100: sum = 1'b1;

3'b111: sum = 1'b1;

default: sum = 1'b0;

endcase

end

endmodule

-

逻辑电路

+关注

关注

13文章

494浏览量

42609 -

Verilog

+关注

关注

28文章

1351浏览量

110066

原文标题:组合逻辑概述与Verilog三种描述形式

文章出处:【微信号:LF-FPGA,微信公众号:小鱼FPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

【技巧分享】时序逻辑和组合逻辑的区别和使用

组合逻辑电路的分析与设计-逻辑代数

组合逻辑电路的设计

组合逻辑电路原理概述及作用分析

组合逻辑电路分析和设计方法,常用的逻辑电路有哪些?冒险现象的概述

数字电路教程之组合逻辑电路课件详细资料免费下载

组合逻辑电路的学习教程课件免费下载

组合逻辑概述

组合逻辑概述

评论