电阻也会有静电能力?电阻会被静电打坏吗?很多人可能报有疑问,本文抛砖引玉的介绍一下电阻的静电能力。

在日常设计中我们很关注半导体器件的静电防护设计,但很少关注电阻是否需要静电防护,以及电阻是否也会被静电打坏而失效。答案是肯定的,不然本文也就没有意义了。

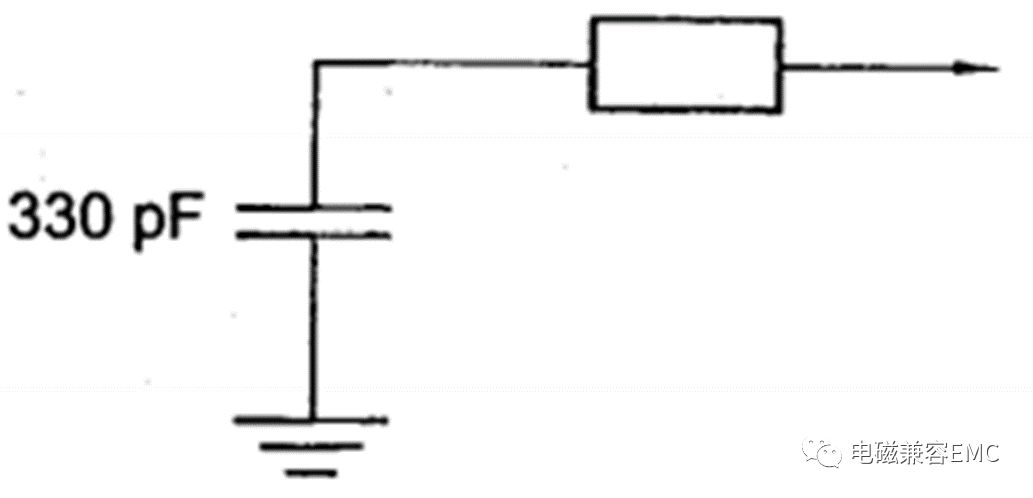

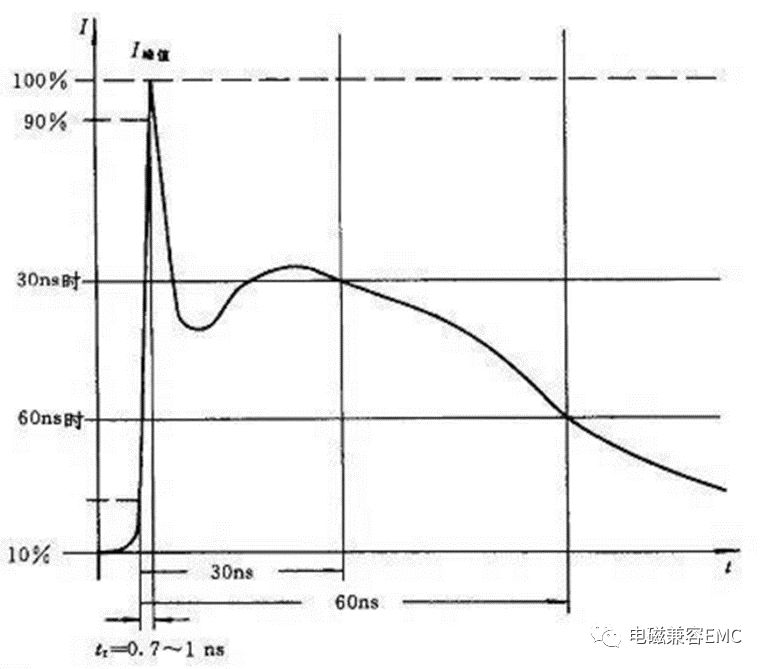

静电有三种模型HDM:人体模型;MM:机器模型;CDM:器件放电模型。本文为分析方便,只选取人体模型作为研究,以下是人体模型的静电放电模型和放电波形(参考ISO10605)。

图1.人体模型及放电波形

首先我们来定义一下何为失效,电阻的失效模式有开路、短路、漂移三种,只要出现任意一种则鉴定为失效,特别是漂移超过规格标定即失效。

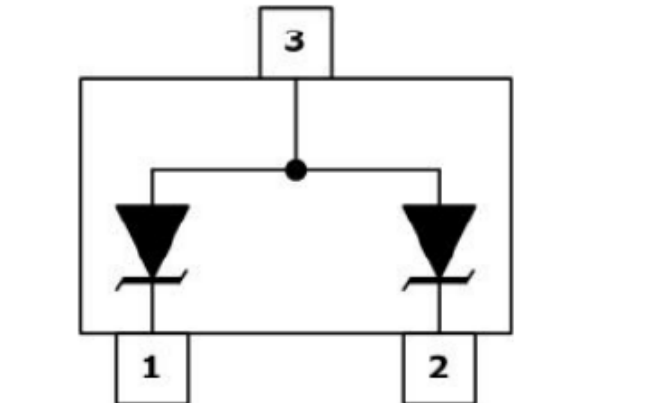

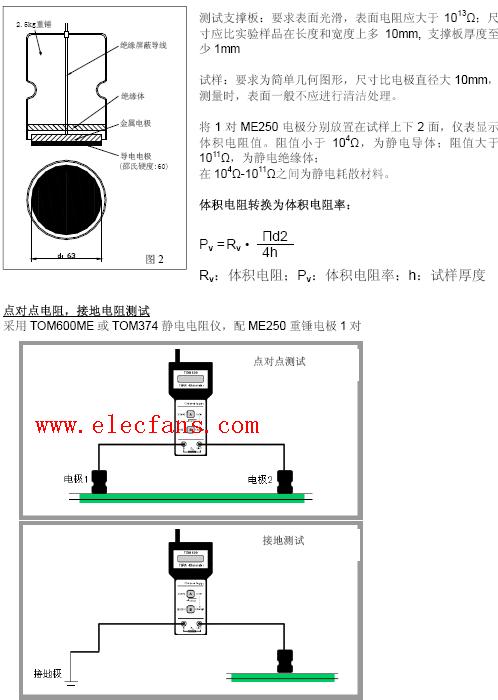

首先来确定电阻的几个重要参数:电压、电流、额定功率及脉冲功率。前三个我想不必赘述,重点说一下脉冲功率,以下图2是一款0603电阻的脉冲功率参数,单脉冲与重复脉冲功率。

以±8kV的人体模型为例:静电放电时间在ns级别,具体参考图1。而下图2中电阻的脉冲功率给出的时间参数最小是1us(10-6),差别不是特别大,在此可近视的取电阻能承受的脉冲功率为额定功率的70-90倍。(注:不同工艺的电阻不一样,在此处是针对性的具体分析)

图2.0603电阻的脉冲功率

假设端口的电阻为10K到地,则电阻实际承受的脉冲功率为:

Pesd=8000V*8000V/10K=6400W >> 90*PR=9W

则电阻有失效风险,典型的失效是电阻会漂移。所以不要以为电阻放端口可以无忧,但其实风险很大,设计时需要注意并加上一定的防护措施。应该保证电阻的脉冲功率能够承受最高的静电放电功率。

-

电阻

+关注

关注

86文章

5539浏览量

172415 -

半导体器件

+关注

关注

12文章

761浏览量

32112

原文标题:电阻的ESD能力研究

文章出处:【微信号:EMC_EMI,微信公众号:电磁兼容EMC】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

CC2540有什么方法改善抗静电能力?

ESD静电阻保护器件的应用

什么是静电保护及技术讲解

防静电元件SM15抗静电和抗浪涌电流能力分析报告的详细概述

手机静电放电抗扰度测试及提高手机抗静电能力的设计参考

静电对LED的危害及LED防静电常识

ESD静电阻抗器产品介绍

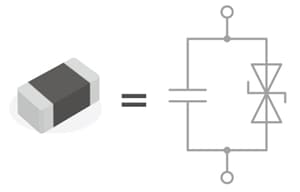

陶瓷电容与ESD二极管防静电能力对比PK

超小封装,超低漏流IR,抗静电能力30KV,超小电压防静电ESD推荐

电阻也会有静电能力?电阻会被静电打坏吗?

电阻也会有静电能力?电阻会被静电打坏吗?

评论