关于层叠和阻抗设计,设计师需要经历的几个阶段

1.小白级:刚接触PCB设计的时候,可能所涉及的产品非常简单不属于高速的范畴,完全不需要控制阻抗,把线拉通就完事了,运气好点的工程师刚涉及PCB设计的时候就能接触高速的产品,但是却不知道要控制阻抗,导致设计出问题;

2.初级:经过一段时间的PCB设计,慢慢了解到阻抗相关的一些概念,具备了高速电路的一些基本知识,知道了控制阻抗的必要性,但是缺乏PCB材料和工艺制程以及阻抗计算相关的一些知识,对阻抗的认识还不是很深,只知道控阻抗需要提供阻抗需求表给板厂给板厂来控。

3.中级:在PCB设计上有一定的经验,知道影响阻抗的各种参数,会用Si9000选择相应的阻抗模型进行阻抗计算,但是对板材和工艺方面的知识欠缺,觉得自己计算阻抗和设计层叠比较繁琐,并且就算在设计阶段做了阻抗计算到了板厂还是要调整,所以还是提供一份阻抗需求表,文字加图片的说明方式让板厂来控。

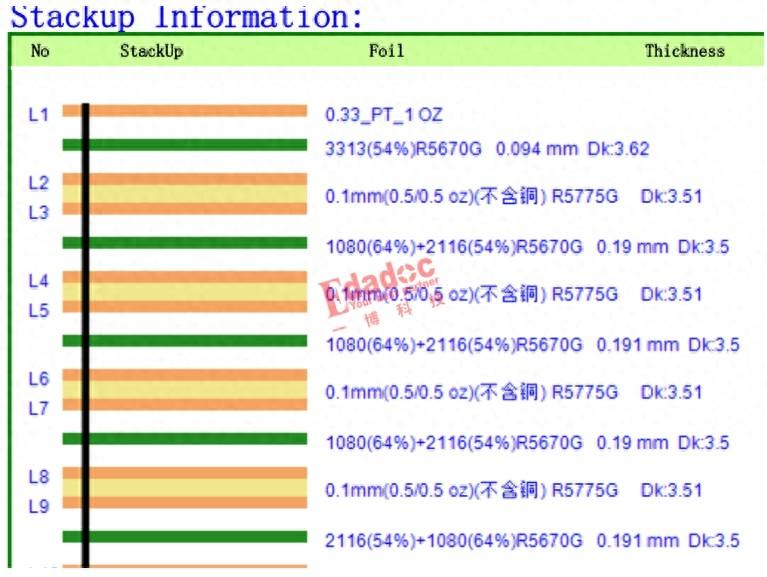

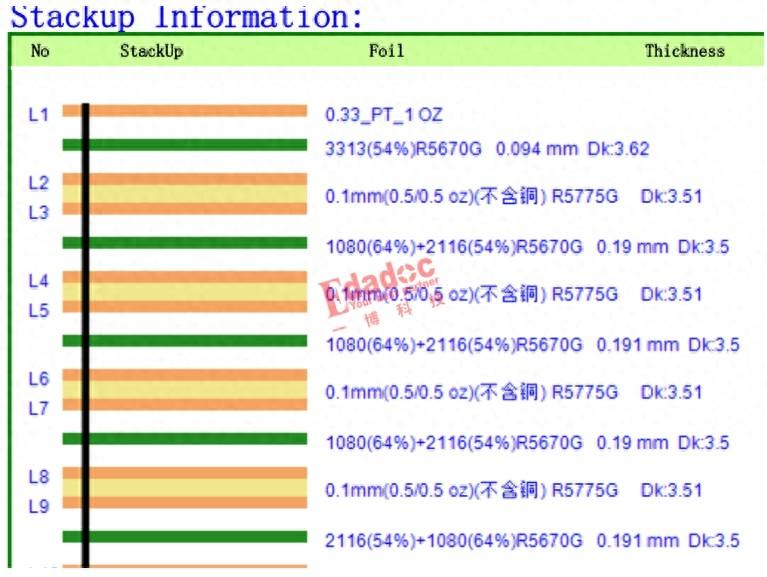

4.高级:对高速PCB设计的有很深的认识,对板厂的加工流程,板材的相关特性及数据有一定的了解,会提供详细的层叠阻抗设计表格,指明层叠顺序的同时,把各层的大致厚度都标注出来,板厂虽然最后一定会调整,但是会在我们指定范围之内做微调。

这个问题你可以回答的诚实一点:)

段位低,找大腿?

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

原文标题:你的层叠和阻抗什么段位?

文章出处:【微信号:PCBTech,微信公众号:EDA设计智汇馆】欢迎添加关注!文章转载请注明出处。

相关推荐

LDC1614EVM一直处于红灯状态,根据资料板子一直在自我测试,但是应该自我测试完之后就可以使用了,一直处于自我测试阶段,不能使用

发表于 01-03 06:53

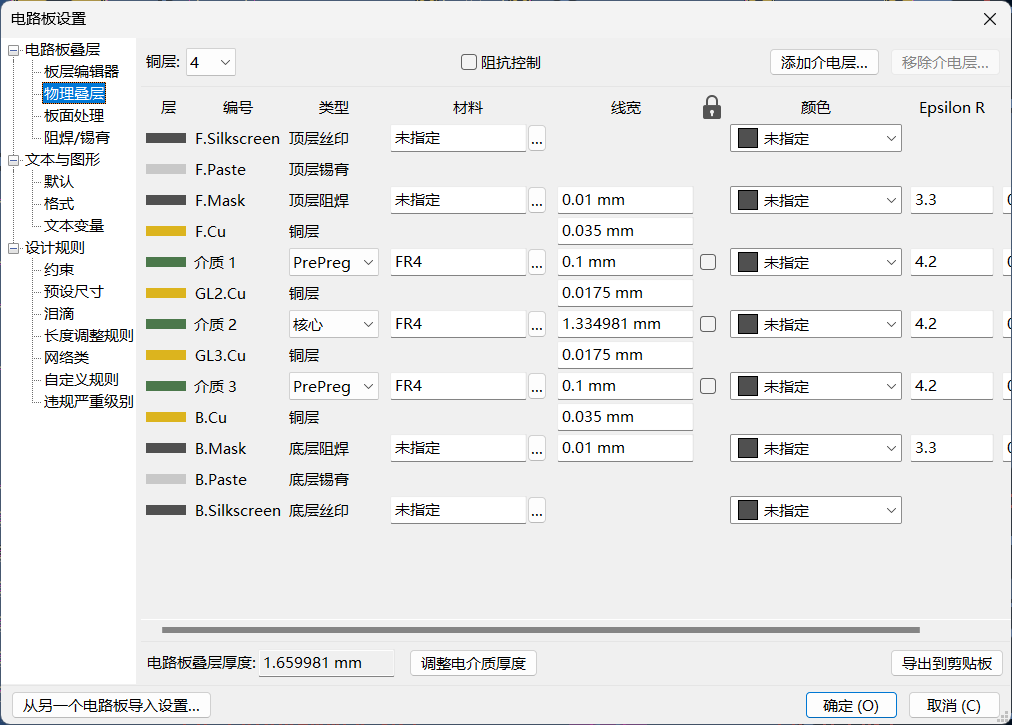

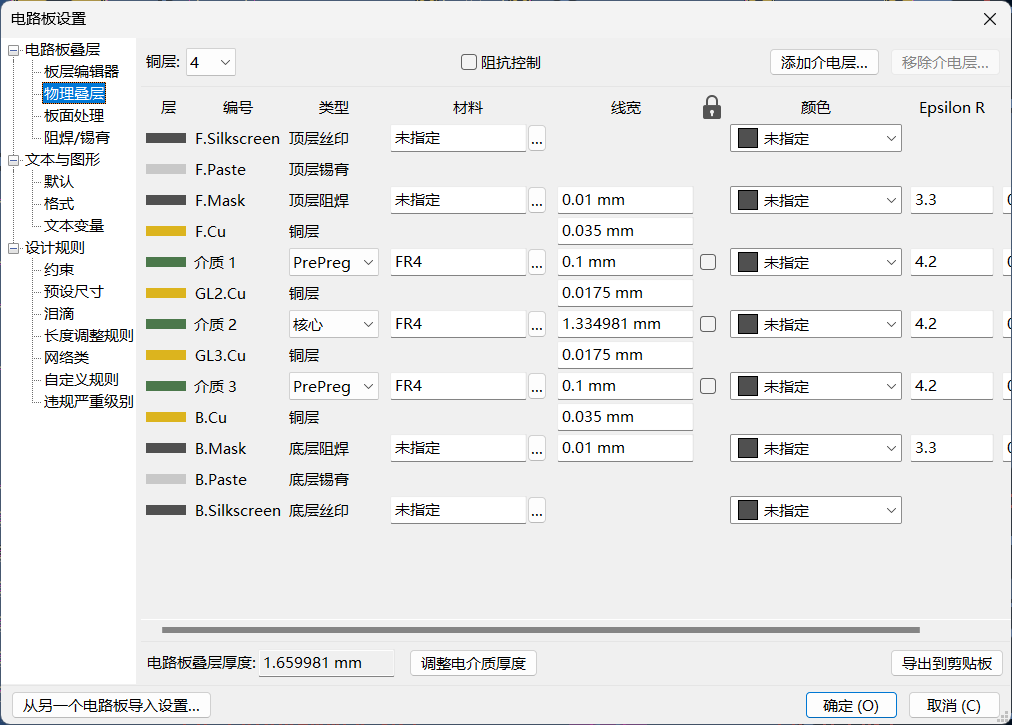

: 物理叠层 首先需要关注的是“物理层叠”。在这里,你要选择 PCB 的层数及层叠结构;如果需要做阻抗,还需要关注 Core 和 Prepreg 的 厚度: 最下方会计算出

![的头像]() 发表于

发表于 12-17 11:20

•531次阅读

阻抗对音频设备的影响 功率传输效率 : 阻抗对功率传输效率有直接影响。在理想情况下,音频设备的输出阻抗应与扬声器的输入阻抗相匹配,以实现最大功率传输。如果

![的头像]() 发表于

发表于 12-10 09:57

•533次阅读

数字反复出现在各种标准、应用说明和设计指南中,好像有什么不一样的魅力。 那为什么是50Ohm,不是40Ohm,60Ohm或者100Ohm? 难道50Ohm真的与众不同吗? 下面我们一起来了解下。 50Ohm这个标准的起源可以追溯到20世纪20年代末至30年代初,当时电信业正处于起步

![的头像]() 发表于

发表于 11-22 10:43

•764次阅读

电子发烧友网站提供《0.5mm层叠封装应用处理器的PCB组装指南,第II部分.pdf》资料免费下载

发表于 10-14 11:09

•0次下载

差分阻抗与单端阻抗是电子电路设计中非常重要的概念,它们在信号传输、信号完整性、电磁兼容性等方面起着关键作用。 差分阻抗与单端阻抗的概念 1.1 差分

![的头像]() 发表于

发表于 07-15 11:09

•2804次阅读

我想知道当ESP8285处于深度睡眠状态时,XPD_DCDC状态是什么。

它是否处于高逻辑水平?

还是在高阻抗下?

换句话说:它是深度睡眠期间的开漏GPIO吗?

发表于 07-15 08:32

在高速PCB设计中,阻抗匹配是至关重要的。过孔作为连接不同层信号的关键元素,也需要进行阻抗匹配以确保信号的完整性。捷多邦小编今天就与大家聊聊PCB阻抗匹配过孔~ 过孔是PCB上用于连接不同层信号线

![的头像]() 发表于

发表于 07-04 17:39

•1532次阅读

一站式PCBA智造厂家今天为大家讲讲PCBA线路板中的阻抗特性与受控阻抗是什么?PCB阻抗特性与受控阻抗原理。在PCBA线路板中,阻抗特性和

![的头像]() 发表于

发表于 06-26 09:20

•1065次阅读

高速PCB层叠确认时,PCB工程确认时不提供铜箔类型,大家认为正常吗,工厂说不提供铜箔类型,是生产时多了一种选择,你能接受吗,请走进今天的案例,了解案例背后的秘密。

![的头像]() 发表于

发表于 06-17 17:16

•495次阅读

。

高速PCB的铜箔类型介绍:

我们高速pcb层叠设计时,常用铜箔有如下几种,HTE RTF 和HVLP。

松下M6G的材料手册上明确标示,有两种铜箔类型,你是否有注意到。

为此大师兄专门找了松下的华

发表于 06-17 16:48

1、输入阻抗

输入阻抗是指一个电路输入端的等效阻抗。在输入端上加上一个电压源U,测量输入端的电流I,则输入阻抗Rin=U/I。你可以把输入端

发表于 06-01 08:08

在电子学和电路理论中,阻抗是一个核心的概念,它描述了电路对电流的阻碍作用。在电路分析和设计中,我们经常遇到输入阻抗和输出阻抗这两个概念。它们分别代表了电路在输入端和输出端对外部电路的阻碍作用。本文将详细探讨输入

![的头像]() 发表于

发表于 05-28 14:33

•3713次阅读

Sora短期不会向公众开放 还处于反馈获取阶段 据外媒报道Sora核心团队在一次采访中透露,Sora短期不会向公众开放,Sora大模型目前还处于反馈获取阶段,还不是一个完善产品;还需要

![的头像]() 发表于

发表于 03-14 14:55

•697次阅读

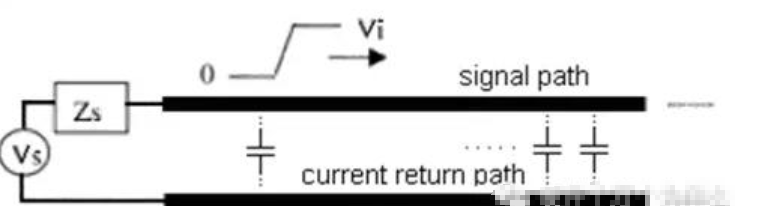

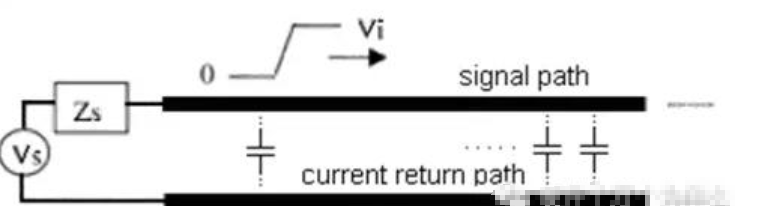

如果传输线具有恒定不变的瞬时阻抗,就称之为传输线的特性阻抗 特性阻抗描述了信号沿传输线传播时所受到的瞬态阻抗,这是影响传输线电路中信号完整性的一个主要因素。如果没有特殊说明,一般用

![的头像]() 发表于

发表于 02-02 17:21

•1282次阅读

你处于层叠和阻抗设计的什么阶段?

你处于层叠和阻抗设计的什么阶段?

评论