今天我们要介绍的时序分析概念是ETM。全称extracted timing model。这是在层次化设计中必须要使用的一个时序模型文件。由block owner产生,在顶层设计使用。

当block owner做完PR以后,需要将block边界上的timing信息抽取出来,存放成一个timing lib文件。这个lib文件就是ETM文件。可以将做完PR的block理解为一个Macro,ETM就是该Macro的lib文件。顶层读入每个block的ETM文件后,就能看到block边界上的timing信息。根据设计阶段的不同,我们可以在preCTS, postCTS以及postRoute之后分别抽取ETM供顶层人员使用,当然越往后阶段的ETM越精确.

来看看ETM文件里有什么内容:

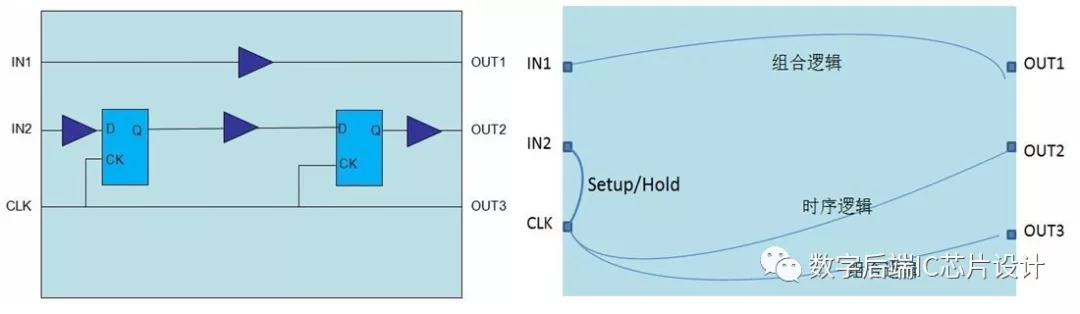

boundary timing arc:包括in2reg,reg2out,in2out三种timing path的信息,reg2reg的path会被忽略

1) In2reg:

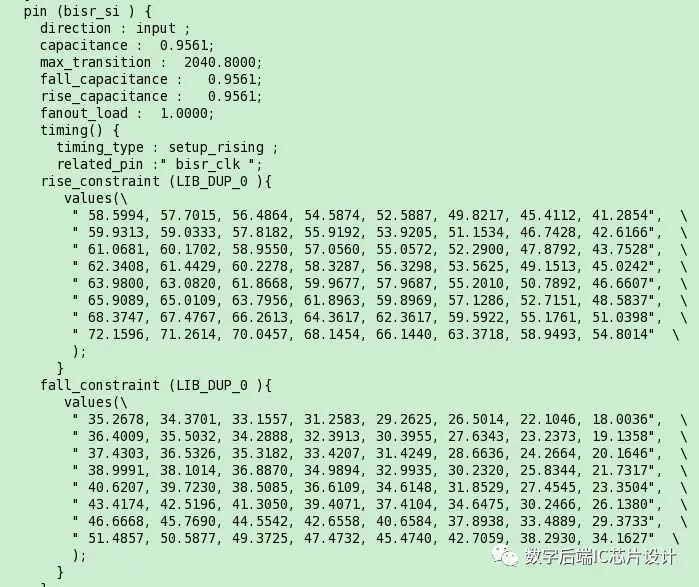

存入ETM中的是setup和hold的arc

Setup arc = data path delay (input to FF) + FF setup value – clock path delay

Hold arc value = data path delay (input to FF) - FF hold value – clock path delay

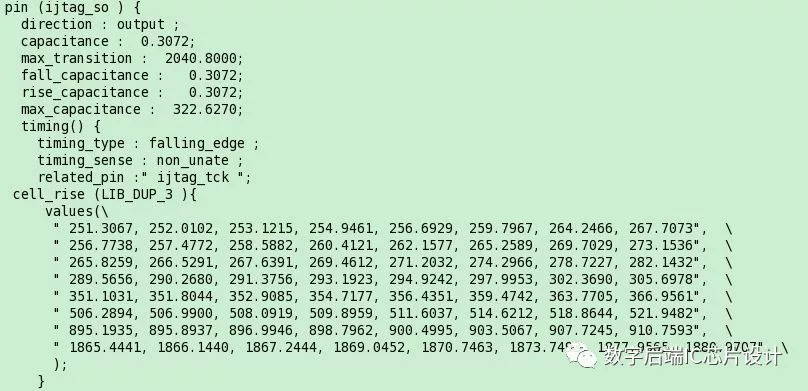

2) Reg2Out

存入ETM中的是时序逻辑的延迟

时序逻辑延迟 = delay (CLK到CK pin) + delay (CK pin到output port).

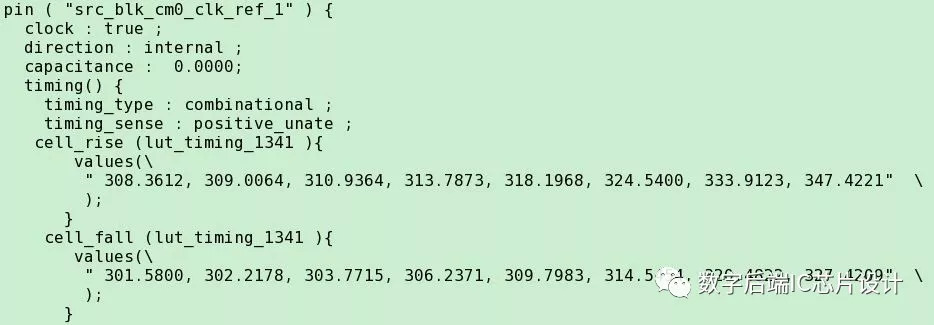

3) In2Out

存入ETM中的是组合逻辑的延迟

组合逻辑延迟 = Path delay

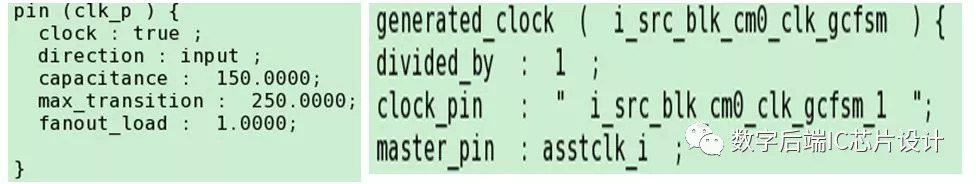

当然,ETM model里还会保存很多内容,比如

Design rule(max fanout, max_transition, max_cap)

Clocks(包括create_clock和generate clock)

Path Exceptions, case constant等,大家有兴趣可以去研究下。

使用方法

PT:extract_model

extract_model -library_cell -output model2 -format {db}

EDI:do_extract_model

do_extract_model -cell_name test_model -library_name test_lib test.lib

-

组合逻辑

+关注

关注

0文章

48浏览量

10084 -

时序分析

+关注

关注

2文章

127浏览量

22624 -

ETM

+关注

关注

0文章

9浏览量

7638

原文标题:时序分析基本概念介绍

文章出处:【微信号:IC_Physical_Design,微信公众号:数字后端IC芯片设计】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

时序分析的基本概念ETM的详细介绍及如何应用的资料概述

时序分析的基本概念ETM的详细介绍及如何应用的资料概述

评论