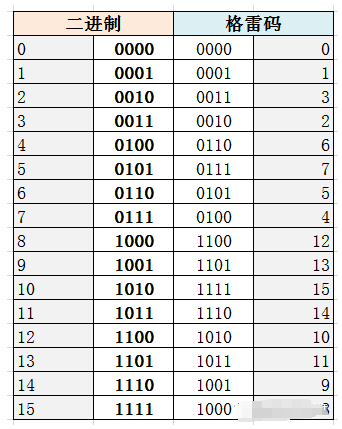

在传递读写时钟域的指针使用格雷码来传递,如何把二进制转换为格雷码,格雷码是如何判断读空写满呢?

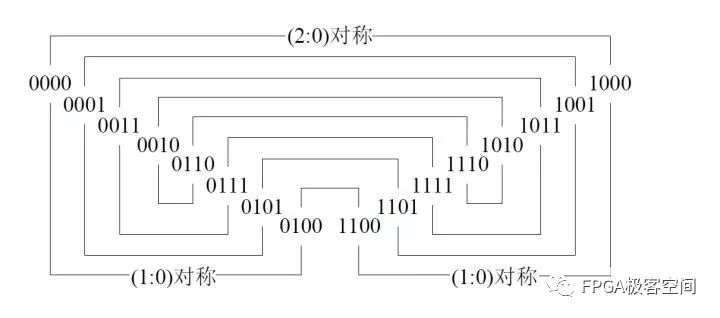

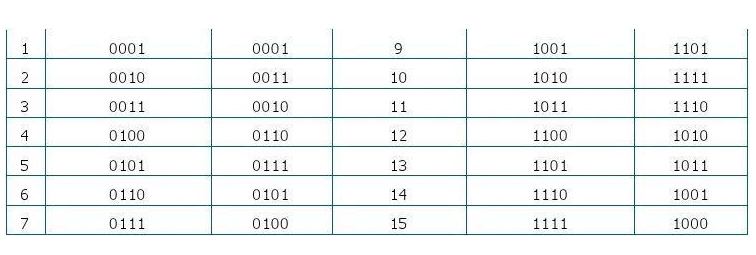

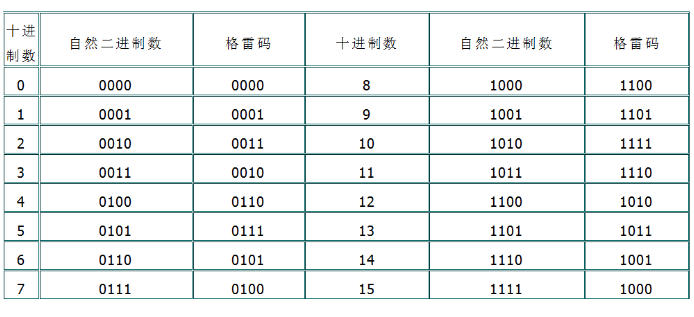

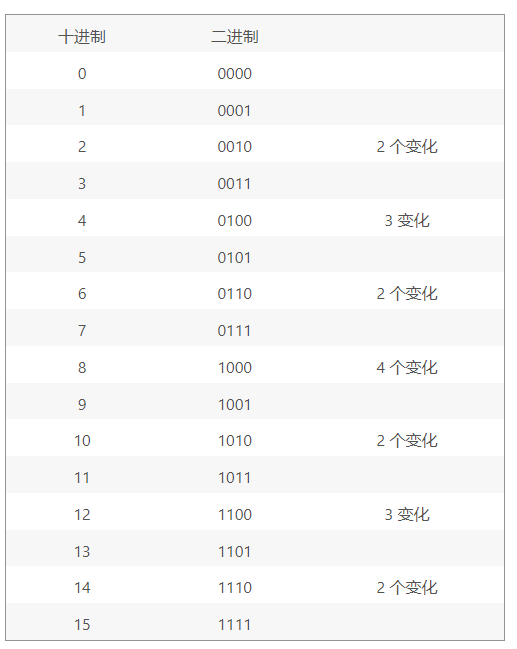

二进制码转换成二进制格雷码,其法则是保留二进制码的最高位作为格雷码的最高位,而次高位格雷码为二进制码的高位与次高位相异或,而格雷码其余各位与次高位的求法相类似。

这样就可以实现二进制到格雷码的转换了,总结就是移位并且异或,verilog代码实现就一句:assign wgraynext = (wbinnext>>1) ^ wbinnext。

因为格雷码与二进制计数的有区别,我们可以得出以下的结论:

当高2bit的相反,后几位的bit相同时,写满;

当写指针等于读指针时,读空。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

二进制

+关注

关注

2文章

809浏览量

43170 -

Verilog

+关注

关注

30文章

1374浏览量

114709 -

格雷码

+关注

关注

2文章

34浏览量

13554

原文标题:异步FIFO格雷码与空满

文章出处:【微信号:ALIFPGA,微信公众号:FPGA极客空间】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

热点推荐

如何把二进制转换为格雷码?格雷码是如何判断读空写满呢?

如何把二进制转换为格雷码?格雷码是如何判断读空写满呢?

评论