设计背景:

二进制转十进制在设计应用中十分的广泛。尤其在AD转化中是必须所用到的一个小知识点,学习二进制转十进制的方法显的非常的重要。今天就和笔者来学习二进制转十进制的方法,通过简单的学习来掌握这么一门知识。

设计原理:

本次的设计主要是一个简单的二选一数据选择器,我们的设计主

二进制中只有 0 和 1 两个状态,可以表示 0、1 两种状态的电 子器件很多,如开关的接通和断开,晶体管的导通和截止、磁元 件的正负剩磁、电位电平的低与高等都可表示 0、1 两个数码。使 用二进制,电子器件具有实现的可行性。

二进制数的运算法则少,运算简单,使计算机运算器的硬件结 构大大简化。由于二进制 0 和 1 正好和逻辑代数的假(false)和 真(true)相对应,有逻辑代数的理论基础,用二进制表示二值 逻辑很自然。电子器件中,所有的数据都是用二进制来表示的。

2.BCD码

BCD 码(Binary-Coded Decimal)亦称二进码十进数或二-十进制代码。用4位二进制数来表示1位十进制数中的0~9这10个 数码。BCD 码是一种二进制的数字编码形式,用二进制编码的十 进制代码。BCD 码这种编码形式利用了四个位元来储存一个十进 制的数码,使二进制和十进制之间的转换得以快捷的进行。

3.实现方法

1)对10求余法

将需要转换的数字除以“权”,然后对10求余,得出数字各个 位上的数字。例如:8’b1000_0000(10进制中的128),将此数 字对10求余,得出个位“8”,然后将“8”赋给最低的4位。将 此数字(128)除以10,得出12(在FPGA计算中,自动取整), 对10求余,然后得出十位“2”,把“2”赋给次低的4位。将此 数字(128)除以100,得出1,对10求余,然后得出百位“1”, 把“1”赋给另外的4位。这样就转换出了BCD码。

这类方法中,利用了大量的除法和求余,占用了大量的逻辑资 源。但是,实现比较简单,如果芯片的逻辑资源足够的话,可以 采取使用这种方法。

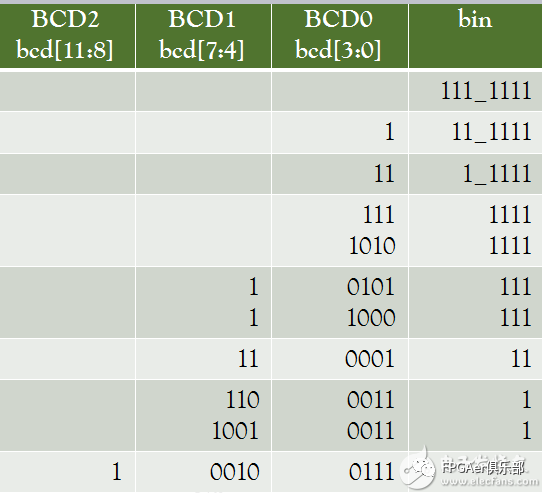

2)大四加三法

进行移位,然后进行判断。如果大于四,则加三。最后得出我们想要的BCD码(下述是按照转换7位讲解的原理)。

架构图如下

bin_data[7:0]:输入的二进制数据。

bin_data[11:0]:输出的BCD码(输入的二进制数据为8位,最大 为8’b1111_1111(255),每四位二进制表示一个BCD码,故而12位)。

设计代码:

设计模块

module bin_to_bcd(bin, bcd);

input [7:0] bin;

output [11:0] bcd;

wire [19:0] shift_reg [5:0];

assign shift_reg[5] = {9'b0,bin,3'b0};

bcd_modify u1(.bcd_in(shift_reg[5]), .bcd_out(shift_reg[4]));

bcd_modify u2(.bcd_in(shift_reg[4]), .bcd_out(shift_reg[3]));

bcd_modify u3(.bcd_in(shift_reg[3]), .bcd_out(shift_reg[2]));

bcd_modify u4(.bcd_in(shift_reg[2]), .bcd_out(shift_reg[1]));

bcd_modify u5(.bcd_in(shift_reg[1]), .bcd_out(shift_reg[0]));

assign bcd = shift_reg[0][19:8];

endmodule

module bcd_modify(bcd_in, bcd_out);

input [19:0] bcd_in;

output [19:0] bcd_out;

wire [19:0] bcd_reg;

bcd_sigle_modify u1(.bcd_in(bcd_in[19:16]), .bcd_out(bcd_reg[19:16]));

bcd_sigle_modify u2(.bcd_in(bcd_in[15:12]), .bcd_out(bcd_reg[15:12]));

bcd_sigle_modify u3(.bcd_in(bcd_in[11:8]), .bcd_out(bcd_reg[11:8]));

assign bcd_reg[7:0] = bcd_in[7:0];

assign bcd_out = {bcd_reg[18:0],1'b0};

endmodule

module bcd_sigle_modify(bcd_in, bcd_out);

input [3:0] bcd_in;

output reg [3:0] bcd_out;

always @ (*)

begin

if (bcd_in > 4)

bcd_out = bcd_in + 3;

else

bcd_out = bcd_in;

end

endmodule

测试模块

`timescale 1ns/1ps

module tb();

reg [7:0] bin;

wire [11:0] bcd;

initial begin

bin = 255;

#500 bin = 20;

#500 bin = 125;

#500 $stop;

end

bin_to_bcd bin_to_bcd_dut(

.bin(bin),

.bcd(bcd)

);

endmodule

仿真图:

从仿真中可以看出本次设计的正确性,测试中我们输出的二进制和为8个1也就是255,转化为10进制后 按16进制显示,也就是255,通过验证设计正确。

-

二进制

+关注

关注

2文章

809浏览量

43222 -

BCD

+关注

关注

1文章

99浏览量

32486 -

十进制

+关注

关注

0文章

68浏览量

13876

原文标题:FPGA学习系列:32. 二进制转十进制的设计

文章出处:【微信号:FPGAer_Club,微信公众号:FPGAer俱乐部】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

FPGA学习系列:32. 如何实现二进制转十进制的设计

FPGA学习系列:32. 如何实现二进制转十进制的设计

评论