IC layout布局经验总结,IC layout Experience

关键字:IC布线经验,PCB布线经验

1 查看捕捉点设置是否正确.08工艺为0.1,06工艺为0.05,05工艺为0.025.

2 Cell名称不能以数字开头.否则无法做DRACULA检查.

3 布局前考虑好出PIN的方向和位置

4 布局前分析电路,完成同一功能的MOS管画在一起

5 对两层金属走向预先订好。一个图中栅的走向尽量一致,不要有横有竖。

6 对pin分类,vdd,vddx注意不要混淆,不同电位(衬底接不同电压)的n井分开.混合信号的电路尤其注意这点.

7 在正确的路径下(一般是进到~/opus)打开icfb.

8 更改cell时查看路径,一定要在正确的library下更改,以防copy过来的cell是在其他的library下,被改错.

9 将不同电位的N井找出来.

布局时注意:

10 更改原理图后一定记得check and save

11 完成每个cell后要归原点

12 DEVICE的 个数 是否和原理图一至(有并联的管子时注意);各DEVICE的尺寸是否和原理图一至。一般在拿到原理图之后,会对布局有大概的规划,先画DEVICE,(DIVECE之间不必用最小间距,根据经验考虑连线空间留出空隙)再连线。画DEVICE后从EXTRACTED中看参数检验对错。对每个device器件的各端从什么方向,什么位置与其他物体连线 必须 先有考虑(与经验及floorplan的水平有关).

13 如果一个cell调用其它cell,被调用的cell的vssx,vddx,vssb,vddb如果没有和外层cell连起来,要打上PIN,否则通不过diva检查.尽量在布局低层cell时就连起来。

14 尽量用最上层金属接出PIN。

15 接出去的线拉到cell边缘,布局时记得留出走线空间.

16 金属连线不宜过长;

17 电容一般最后画,在空档处拼凑。

18 小尺寸的mos管孔可以少打一点.

19 LABEL标识元件时不要用y0层,mapfile不认。

20 管子的沟道上尽量不要走线;M2的影响比M1小.

21 电容上下级板的电压注意要均匀分布;电容的长宽不宜相差过大。可以多个电阻并联.

22 多晶硅栅不能两端都打孔连接金属。

23 栅上的孔最好打在栅的中间位置.

24 U形的mos管用整片方形的栅覆盖diff层,不要用layer generation的方法生成U形栅.

25 一般打孔最少打两个

26 Contact面积允许的情况下,能打越多越好,尤其是input/output部分,因为电流较大.但如果contact阻值远大于diffusion则不适用.传导线越宽越好,因为可以减少电阻值,但也增加了电容值.

27 薄氧化层是否有对应的植入层

28 金属连接孔可以嵌在diffusion的孔中间.

29 两段金属连接处重叠的地方注意金属线最小宽度

30 连线接头处一定要重叠,画的时候将该区域放大可避免此错误。

31 摆放各个小CELL时注意不要挤得太近,没有留出走线空间。最后线只能从DEVICE上跨过去。

32 Text2,y0层只是用来做检查或标志用,不用于光刻制造.

33 芯片内部的电源线/地线和ESD上的电源线/地线分开接;数模信号的电源线/地线分开。

34 Pad的pass窗口的尺寸画成整数90um.

35 连接Esd电路的线不能断,如果改变走向不要换金属层

36 Esd电路中无VDDX,VSSX,是VDDB,VSSB.

37 PAD和ESD最好使用M1连接,宽度不小于20um;使用M2连接时,pad上不用打VIA孔,在ESD电路上打。

38 PAD与芯片内部cell的连线要从ESD电路上接过去。

39 Esd电路的SOURCE放两边,DRAIN放中间。

40 ESD的D端的孔到poly的间距为4,S端到poly的间距为^+0.2.防止大电流从D端进来时影响poly.

41 ESD的pmos管与其他ESD或POWER的nmos管至少相距70um以上。

42 大尺寸的pmos/nmos与其他nmos/pmos(非powermos和ESD)的间距不够70um时,但最好不要小于50um,中间加NWELL,打上NTAP.

43 NWELL和PTAP的隔离效果有什么不同?NWELL较深,效果较好.

44 只有esd电路中的管子才可以用2*2um的孔.怎么判断ESD电路?上拉P管的D/G均接VDD,S接PAD;下拉N管的G/S接VSS,D接PAD.P/N管起二极管的作用.

45 摆放ESD时nmos摆在最外缘,pmos在内.

46 关于匹配电路,放大电路不需要和下面的电流源匹配。什么是匹配?使需要匹配的管子所处的光刻环境一样。 匹配分为横向,纵向,和中心匹配。

21为纵向匹配,12为中心匹配(把上方1转到下方1时,上方2也达到下方2位置)21中心匹配最佳。

47 尺寸非常小的匹配管子对匹配画法要求不严格.4个以上的匹配管子,局部和整体都匹配的匹配方式最佳.

48 在匹配电路的mos管左右画上dummy,用poly,poly的尺寸与管子尺寸一样,dummy与相邻的第一个poly gate的间距等于poly gate之间的间距.

49 电阻的匹配,例如1,2两电阻需要匹配,仍是1221等方法。电阻dummy两头接地vssx。

发布评论请先 登录

相关推荐

TLV320AIC33IRGZ Layout走线时需要注意的事项有哪些?

Layout设计有哪些注意事项

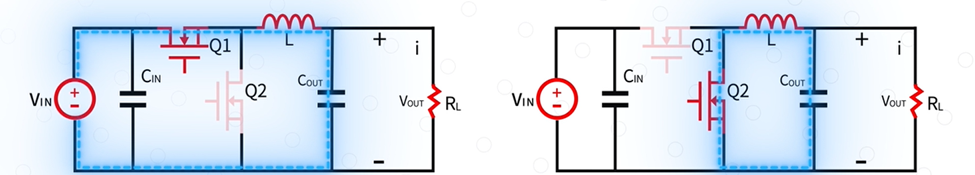

Buck电路中PCB layout布局设计和注意事项

PADS Layout 技术问题

PCB Layout 的 9 个套路

各位大佬,帮忙看下这是什么问题?Router打不开对应psda的pcb文件,layout布局后,点router后,就报这个错。版本vx.2.3

PMP20587.1-反相降压/升压 PCB layout 设计

ADS应用技巧(16)—Layout连接性模式选项

IC layout布局经验总结,IC layout Experience

IC layout布局经验总结,IC layout Experience

评论