引 言

随着消费类电子,如MP3、3G手机、视频终端以及宽带无线网络的普及,对大容量存储设备的需求越来越强烈。传统的SRAM、SDRAM以及DDR SDRAM等存储设备的价格与容量比,远远比硬盘高;光存储设备虽然更加廉价,但是在便携性上却远逊于硬盘解决方案。现在硬盘厂商提供了各种适用于不同用途的廉价海量存储设备,如1 in(英寸)的微硬盘可以应用于各种小巧的便携设备中,2.5in硬盘可以应用于笔记本和移动存储中,3.5in硬盘可以应用于个人PC和工业自动化中等等。

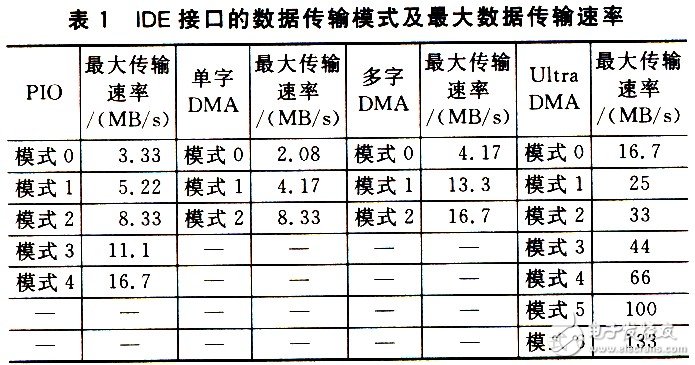

目前,硬盘支持的最为广泛的IDE接口协议中,规定了PIO、DMA以及Ultra DMA三种数据传输模式,其传输速率PIO《多字DMA《Ultra DMA,如表1所列。随着各种多媒体应用的广泛普及,各种设备不但要求拥有海量存储能力,在完成各种实时业务时对数据的传输速率也提出了严格的要求。

现阶段的设计研究主要集中于单边沿锁存数据的PIO和DMA传输模式。大多数设计主要用PIO模式完成控制命令的写入和读取操作,采用DMA数据传输模式进行直接内存读取操作,提高数据传输的速率。如果在相同系统中使用Ultra DMA数据传输模式,则可以在不提高系统时钟频率的基础上,将系统数据传输速率提高l倍,极大地改善了系统性能,而不需要付出更多的硬件资源。因而硬盘的Ultra DMA数据传输方式在工业自动化、Internet网络、消费类电子和各种嵌入式系统中的需求会不断增加,有着很好的商业前景。

1 Nios系统介绍

该设计是在Altera公司推出的Nios嵌入式系统的平台上,设计可以通过Ultra DMA数据传输方式进行高速硬盘读写的接口模块,并开发出相应的IP核。

1.1 Nios系统结构

Nios嵌入式处理器系统通常由N1os处理器、Avalon交换结构总线和各种外围设备(存储、接口及功能模块)的IP核三部分构成。Altera的SOPC Builder系统开发工具可以自动生成这些组件以及连接它们的总线。

Nios处理器是32位结构可配置并包含五级流水线的通用RISC微处理器,采用改进的哈佛存储器结构;处理器带有分离的数据和程序存储器总线控制,具备高速缓存、中断处理功能。与传统处理器相比,Nios指令系统可通过自定义指令和标准处理器选项,利用硬件来明显提高系统性能。

Avalon交换结构总线是Altera开发的用于Nios嵌入式处理器的参数化接口总线,由l组预定义的信号组成,用这些信号可以连接1个或多个IP模块。Altera的S0PC Builder系统开发工具自动地产生Avalon交换结构总线逻辑,其实现只需要极少的FPGA资源,提供完全同步的操作。

Nios嵌入式处理器系统中的各种存储模块、接口模块和功能模块等都在Altera的标准外围设备库中以IP核的方式提供使用,或是由用户自行设计添加到库中,以IP模块的方式在系统中复用。

实现硬盘高速访问功能模块的设计,实际上是在设计一个完整的IP模块,再在Altera提供的SOPC Builder开发环境的设备库中集成该IP核,以达到设计的目的。

1.2采用Nlos软核处理器构建系统的原因

①与其他的实现方式相比有着更好的性能价格比。最常见的硬盘读取控制和数据传输方式是通过单片机或是DSP来实现的,使用单片机或DSP中的PIO接口可以很方便地完成单边沿锁存数据的硬盘PIO和DMA数据传输方式,但在实现双边沿锁存数据的Ultra DMA传输方式时,必须在单片机和DSP芯片外添加额外的FPGA芯片,完成Ultra DMA双边沿锁存数据到单边沿锁存数据的转换,增加了系统设计的成本和复杂性。而采用Nios软核处理器完成与硬盘的Ultra DMA传输方式时,不需要添加任何额外的芯片,仅使用FPGA内的其他资源就可以方便地实现双边沿到单边沿的转换工作。

②与传统的单片机或DSP实现方式相比,Nios嵌入式系统的设计与实现更加简单。从性能上来说,Nios软核处理器与ARM、Intel等的CPU处于同一级别,都能够满足设计的需要,即使是复杂逻辑系统的设计也可以在一片Cyclone或是StratiX芯片上实现全部功能。而且通过使用Altera公司提供的SOPC Builder开发工具,在IP复用的基础上可以快速开发出完整的系统解决方案。

③与传统的单片机或DSP实现方式相比,Nios嵌入式系统的可扩展性更好。单片机或DSP内的资源是硬件厂商固化在芯片内的,用户不可能自行添加或删减,在设计时的灵活性受到器件本身的限制;而Nios软核处理器的所有资源都可以任意地添加或删减,只需最终通过电缆下载到FPGA芯片内就可定制出整个系统的功能。因而在基于Nios的系统设计中,通过对设计文件的修改就可以很方便地进行系统功能的扩展。

2 系统的硬件实现

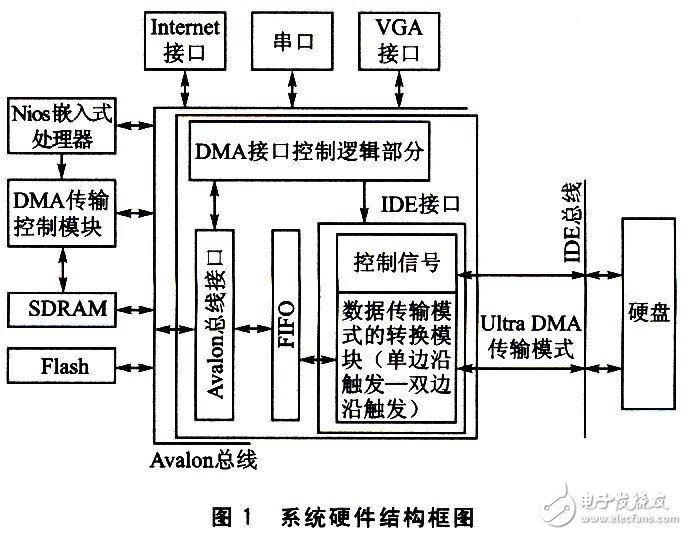

硬件部分由Nios嵌入式系统、Nios与硬盘的接口模块和其他外围接口电路三部分组成,如图1所示。其中设计的核心部分是Nios系统与硬盘接口模块的IP核设计,主要完成数据传输模式的转换,以及对硬盘的控制与操作两部分任务。Nios嵌入式处理器系统的任务是进行整体控制与协调,并对数据进行处理和暂存;外围接口电路主要用来扩充系统的功能,扩大系统的适用范围。

Nios嵌入式处理器系统由Nios嵌入式处理器、DMA控制器、数据存储区SDRAM、程序存储区F1ash和Avalon总线构成。其中DMA控制器用于实现两个存储器之间,或者存储器和外设之间,或者是两个外设之间的直接数据传输。DMA模块用于连接支持流模式传输的外设,并允许定长或变长的数据传输,而不需要CPU的干涉。在Ultra DMA数据传输的过程中,可以一次性传输最多256个扇区的数据,所以在系统中使用DMA控制器可以方便地在硬盘与系统中各种支持流传输模式的设备之间建立直通连接,提高系统的数据传输效率。

外围接口电路主要用于系统功能的扩充,如Internet接口可以使系统方便地接人到网络中提供诸如音乐或视频下载、信息共享等服务;串口用于与计算机或其他设备的互连;VGA接口用于视频信号的输出,在系统外部显示图像等等。

硬盘接口部分主要由接口控制逻辑、Avalon总线接口、FIFO和硬盘IDE接口4部分组成。其中接口控制逻辑部分用于对Nios处理器的指令进行译码并执行相应的操作,控制Ultra DMA传输时的握手和控制信号的产生,协调数据传输过程中IDE接口的硬盘数据速率同Avalon总线接口速率的匹配。

FIFO用于数据的缓冲,解决Avalon总线和IDE接口之间的数据速率不匹配问题。在设计中需要对硬盘UltraDMA的六种数据传输模式同时提供支持,而其传输速率却完全不同,必须添加缓冲区用于数据的暂存。

Avalon总线接口用于与Nios处理器系统相连,传输Nios处理器的指令给控制逻辑部分,以及与系统中的其他部分在DMA控制器的协调下完成数据的传输。

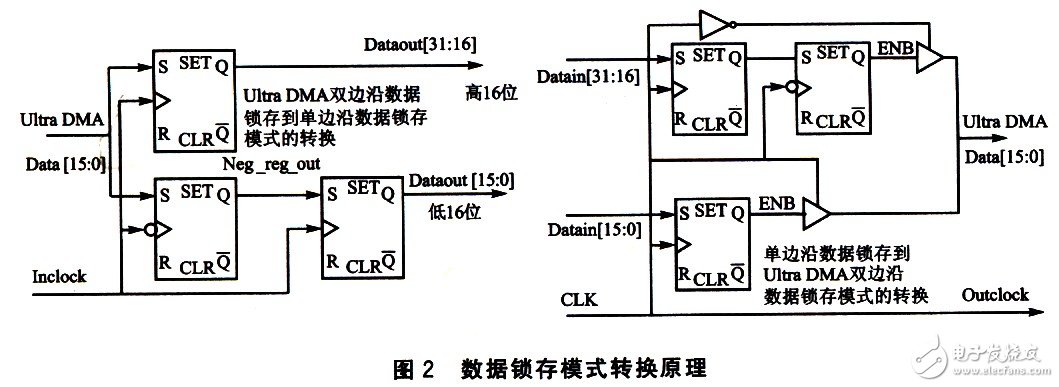

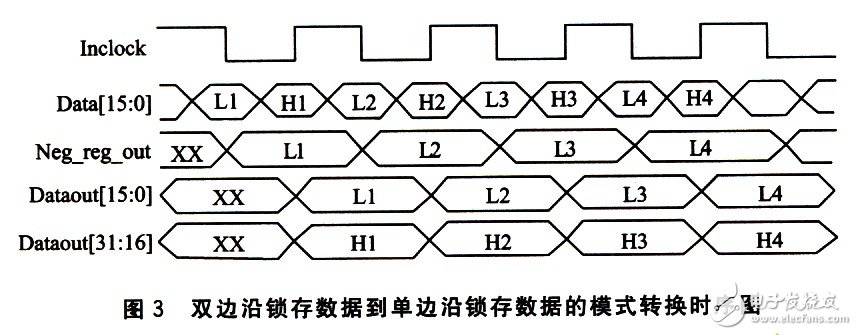

硬盘IDE接口部分除输出控制信号并对硬盘返回的信号做出响应外,还要完成单边沿数据锁存模式与双边沿数据锁存模式相互转换的任务,如图2、图3所示。

由于Nios系统内部数据传输时,都使用时钟上升沿来锁存数据;而IDE总线上传输的Ultra DMA数据,在Clock信号的上升沿和下降沿都有数据需要锁存。因而硬盘接口部分两侧的数据,在传输时工作模式各不相同,需要进行必要的缓冲和模式转换。

数据锁存模式转换模块,用于在IDE总线上双边沿锁存数据和系统内部单边沿锁存数据之间进行锁存模式的转换,这是系统设计的核心问题之一。具体来说,就是在读取硬盘数据时需要将IDE总线上传输的双边沿锁存数据转换为系统内部使用的单边沿锁存数据;在写硬盘操作时完成相反的任务。在设计时采用两组寄存器对不同时钟沿的信号进行锁存,在时钟频率不变的基础上,通过数据带宽的扩展,完成双边沿到单边沿的转换功能;在单边沿数据到双边沿数据的转换过程中,采用相反的构架。

3 系统工作流程

系统在完成基于Ultra DMA的数据传输模式的硬盘访问功能时,需要实现对硬盘数据通过Ultra I)MA模式进行的读操作和写操作。其具体的工作流程各不相同,主要区别在于:

①Nios系统内部的协调过程。作为系统处理核心的Nios处理器,必须向硬盘接口逻辑和DMA控制器中发送指令,使其按照设计要求执行相应的操作。向硬盘接口逻辑部分发送读写硬盘的指令时,需要首先命令读操作时使用FIFO对硬盘数据进行缓冲,在写操作时将FIFO中的缓冲数据发送到硬盘中完成写入操作;向DMA控制器部分发送指令,协调接口缓冲区FIFo和系统内存SDRAM中数据的交互过程,以完成对硬盘的读写操作。

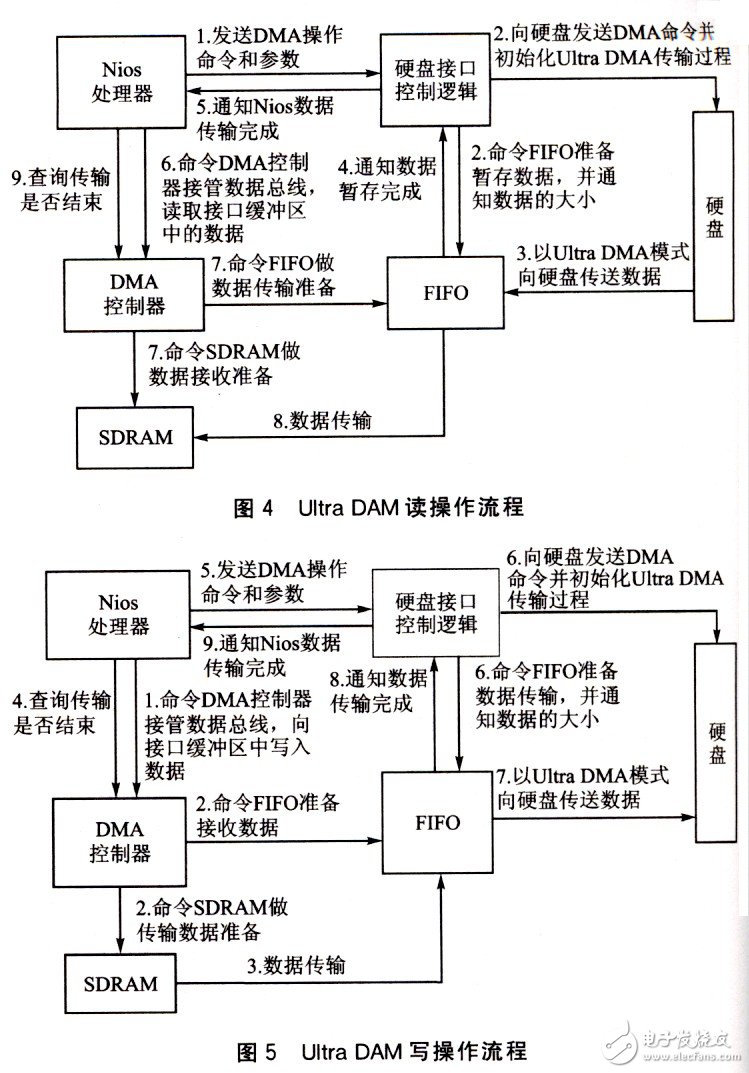

②对硬盘的读写访问操作。在对硬盘进行读写操作时,必须向硬盘的接口寄存器中发送DMA读指令或写指令,其指令码和操作顺序也不尽相同,如图4、图5所示。

4 系统的软件实现

在Nios SDK Shell环境下,使用带Monitor的bootloader程序,可以在程序Debug的同时监控内部存储器的变化,便于硬件设计的检查和程序的调试。软件的编写主要采用C语言,部分嵌入了汇编语言。整个系统软件设计中的重点是以下两部分。

(1)Nios系统内DMA控制器的编程

在DMA传输过程中需要完成的操作有:①配置DMA控制器;②软件启动DMA外设,开始DMA传输;③DMA控制器的主设备读端口从目标地址读取数据,主设备写端口向目标地址写入数据;④DMA传输结束。

这一过程中,需要向DMA控制器的寄存器中写入控制指令来开启一次数据传输过程。要求初始化的寄存器有:status、readaddress、wi rte£Jddress、length和contiol。之后调用系统提供的DMA子程序开启一次DMA操作,使用的DMA子程序有:nr_dma_opy_1_tO_rarlge(在原地址和目标地址之间,传输length长度的数据,原地址固定,而目标地址在每次传输后增加),用于完成数据读取操作时,从FIFO缓冲区中向SDRAM里传输数据;nr_dma_copy_range_to_l(在原地址和目标地址之间,传输lengt长度的数据,目标地址固定,而原地址在每次传输后增加),用于完成数据写操作时,从SDRAM里向FIFO中缓冲数据。

(2)硬盘的DMA读写命令

在对硬盘进行读写操作时须向硬盘的寄存器内写入DMA读指令(或写指令)和相应参数后才可对硬盘中的数据进行访问。在ATAPI 协议中规定了READ DMA指令和WRITE DMA指令的命令格式,需要向SectorCbunt、SectorNulmber、CyclindeLow、CyblindelrHigh、Device/Head、Command寄存器中写入参数和命令代码。其中读指令的代码是C8h、写指令的代码是CAh。在写入命令后就可以对硬盘中的数据进行读写操作。

结 语

本系统使用Nios嵌入式系统在单芯片内实现了数据处理、存储访问、数据模式转换等多个功能。采用Altera公司提供的Quartus II 和 SOPC Builder开发工具可以在完成接口功能设计后,快速进行系统的集成设计和系统仿真,最终可以在Altera提供的Cyclone系列芯片上实现整个系统设计。对Nios处理器重新编程可以在不改变系统硬件框架的基础上,方便地增加系统的功能和处理效率,对系统的升级和再开发有很大的便利。

责任编辑:gt

-

芯片

+关注

关注

455文章

50812浏览量

423598 -

嵌入式

+关注

关注

5082文章

19126浏览量

305178 -

无线网络

+关注

关注

6文章

1435浏览量

65943

发布评论请先 登录

相关推荐

基于 DSP-dMAX 的嵌入式 FIFO 数据传输系统设计

基于单片机和GPRS模块的嵌入式无线数据传输终端的实现方案

DMA进行数据传输和CPU进行数据传输的疑问

数据传输的通信系统设计

基于嵌入式TCP IP的实时数据传输

嵌入式GPRS数据传输终端设计

DMA数据传输(源代码分享)

DMA数据传输在SPEAR300实现高速串口驱动设计

使用Nios嵌入式系统在单芯片上完成Ultra DMA数据传输模式的访问

使用Nios嵌入式系统在单芯片上完成Ultra DMA数据传输模式的访问

评论