当资料传输速率位于400Mbps至1.5Gbps之间时,信号路径(signal path)就会形成传输线(transmission line)。在这个传输速度范围内,信号路径模型必须包括电缆或底板中的电抗性寄生分量。高速资料传输带来的问题不仅仅是资料传输速率本身的问题,快速的信号边缘变换率包含甚至更高的频率分量,这些高频分量在分布式阻抗环境中的传输性能更差。对于200Mbps以上速率的信号,如果忽略寄生阻抗和阻抗不连续性的问题,将会在传输线上产生增加性噪音,并出现资料位元误码。

高速信号传输实例分析

面对上述的问题,我们以基础型高画质(High-Definition,HD)数字视频路由器的处理方式为例进行解说。HD视频路由器可管理来自于广播、工作室或者节目制作设备之间的多项HD节目来源资料串流。HD视频管道是在270Mbps到高达1.485Gbps的速率范围内运作,它需要被仔细地设计并採用一致的设计方法,以确保交换路由器系统不会降低视频资料的完整性。

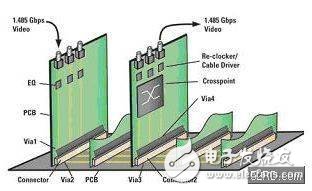

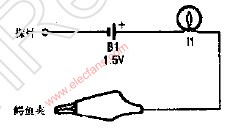

图1︰高画质视频路由器图解。

在图1的这个系统中,可适应均衡器(EQ)直接由BNC连接器接收HD信号。一个公共底板将信号从输入卡连接到开关卡,以输出到目标信号管道。信号从EQ经过近8英寸的PCB,点对点传输到底板连接器,然后透过3到15英寸的底板(长度取决于所使用的插槽类型)传输到第二个连接器,之后再经过8英寸的PCB到交叉点开关元件的输入。一个重组时脉(re-clocker)/线缆驱动器直接连接到交叉点开关的输出以驱动信号在电缆上的传输。这些HD视频路由器系统已模组化,可能具有8个到1000个输入/输出信号管道。也因为如此,信号密度可能非常高。

图2︰信号路径上阻抗TDR图实例。

一般的FR4电路板材料是属于阻抗一致的环境,但是分散式寄生阻抗对讯号质量会产生负面的影响。影响最大的部份,是因大量工作在高于基本的资料速率的频率分量产生的快速上下边缘变换率,所引起的信号损耗和缓慢转换时间。除此之外,在元件间(例如BNC连接器、积体电路、电路板不同层之间的过道孔,或者板子之间的连接器)的互相联结可能导致与特征阻抗(Z0)的阻抗误配,这也会影响到信号品质(如图2)。密集的底板连接器会为讯号路径增加感性负载,而PCB的过道孔增加了信号路径的容性负载。

在信号传输路径上,任何存在阻抗改变的地方都可能出现信号反射。这些反射和寄生阻抗将导致信号幅度的损耗、环状波、上升时间变长和EMI等问题。在本文的范例系统中,从EQ输出到交叉点开关的输入之间FR4电路板长度预计长达31英寸,在这个路径上H会出现几个阻抗不连续的情况。如果沿着这个路径的入射边缘(incident edge)速度为175到200 ps/英寸,资料速率为1.485Gbps(半波长 = 343 ps),那么在任何所给予的时间都存在多达18个传换边缘。阻抗不匹配的入射边缘产生的反射,将影响到信号路径上出现的所有信号变换边缘。从信号边缘1到信号边缘17的反射在到达信号路径终端时,将使第18个信号边缘严重地失真。结果得到的眼形图(图3)显示了幅度损耗、额外的抖动以及上升/下降时间变化。

图3︰经过长达31英吋的FR4电路板传输后,交叉点开关输入处的眼形图。

提升信号传输品质的方法

对于这种挑战的一个解决方案是在子卡和底板之间使用高品质的连接器,这将使连接器的不连续性最小。更好的过道孔设计将进一步使TDR测量图扁平化,如此一来,将使得这个长度的信号路径的实际阻抗将与Z0非常接近。

另外一种更具成本效益的解决方案,是使用一个简单的LVDS缓冲器来驱动和接收底板上传来的信号。它会将信号传输路径再细分为很短的区段,以遮蔽阻抗误配的问题,并减少信号衰减。

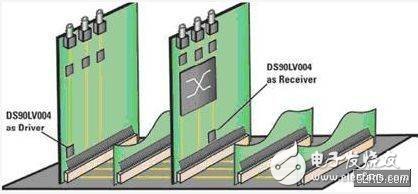

在子卡的边缘放置一个缓冲器以驱动连接器和底板,再透过交换子卡上的另外一个缓冲器用来接收信号(图4),并重新驱动这些信号到交叉点开关的输入,以有效地隐藏两个缓冲器之间的阻抗不连续(图5)。正确的阻抗终结也能确保接收器吸收线路中的所有能量,使这些信号不会反射回来源端。

图4︰利用缓冲器来克服阻抗的不连续问题。

图5︰采用缓冲器隔离底板连接后在交叉点输入的信号眼形图。

除此之外,缓冲器通常还能增强信号品质,改善原始信号。举例而言,具有输入均衡的缓冲器将在底板上传输信号之前消除媒质损耗带来的定量性抖动(deterministic jitter)。输出已预先加强信号的功能可增大信号幅度,使得在交叉点输入或接收器处的眼形图更为开阔。在缓冲器I/O上,较高的ESD极限可保护子卡上的其他元件免受底板上其他位置发生的ESD意外事件而损坏。

LVDS缓冲器的功能

下面将以一种四通道1.5 Gbps LVDS的缓冲器/中继器为例进行说明。该元件的高速资料路径和直通管脚使元件内部产生抖动最小,并简化电路板设计。其可配置的预先加强信号功能,可以克服底板和电缆损耗带来的ISI抖动效应。位差输入和输出在内部用100Ω的电阻终结以改善性能,并减小电路板尺寸。增强信号强度的中继器功能对于在高损耗的电缆和底板上长距离传输信号来说,特别有用。

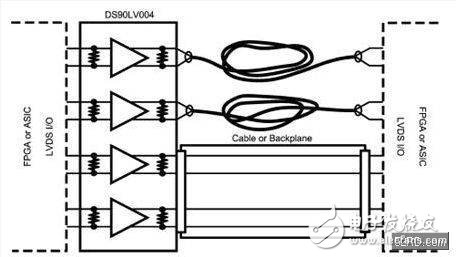

图6︰四通道1.5 Gbps LVDS的缓冲器/中继器典型应用。

LVDS缓冲器具有带电插接保护及15kV静电释放保护功能,可以加强底板及电缆的抗干扰能力,能保证现场可编程式阵列(FPGA)及专用积体电路(ASIC)传送的信号的完整性。其应用范围包括电信、资料通信、工业系统、医疗设备、汽车电子系统及办公室图像系统等,典型应用如图6所示。LVDS缓冲器可以透过普通的底板或简单的电缆配置驱动4个LVDS时钟及/或资料通道。由于这款晶片的位差输入电压范围较宽,因此很易接受LVDS、低电压正射极耦合逻辑(LVPECL)或电流模式逻辑的输入电平,而且输出电平完全符合LVDS的规格要求。

做为范例的LVDS缓冲器晶片的资料传输率高达1.5Gbps,而且系统设计工程师更可利用这款晶片的可配置输出预增强功能将输出加以“加强驱动力”,以便为容易出现信号损耗的互连线路提供补偿。此外,对于必须尽量节省用电的应用(如冗余应用),若晶片的4条通道都暂停操作,系统可以透过低功耗模式将功耗降至最低。

总结

跨底板的高速介面需要在整个信号路径上控制阻抗。采用简单型LVDS缓冲器来隔离阻抗不连续或者缩短互联长度可以降低系统成本;并且也因为不需使用高成本的高频连接器,进一步提升介面的运作效能。

-

缓冲器

+关注

关注

6文章

1923浏览量

45546 -

路由器

+关注

关注

22文章

3737浏览量

114066 -

lvds

+关注

关注

2文章

1043浏览量

65870

发布评论请先 登录

相关推荐

PCB设计阻抗不能连续怎么办?

如何解决PCB设计中阻抗不连续问题

如何解决PCB设计中阻抗不连续问题

如何解决PCB设计中阻抗不连续问题

PCB设计阻抗不连续的原因及解决方法

CDCLVD1208 2:8低加性抖动LVDS缓冲器数据表

CDCLVD1212 2:12低加性抖动LVDS缓冲器数据表

CDCLVD1213 1:4低加性抖动LVDS缓冲器数据表

CDCLVD1204 2:4低加性抖动LVDS缓冲器数据表

采用简单型LVDS缓冲器解决高速信号阻抗不连续性的问题

采用简单型LVDS缓冲器解决高速信号阻抗不连续性的问题

评论