星务中心计算机是微小卫星电子系统的核心部件之一,本文介绍的星务中心计算机是由双TSC695F处理器加外围功能模块实现的,它的主要作用是诊断整星状态、安排整星任务的运行和调度,使卫星能正常的运行。另外,为了减少地面干预次数和增强卫星在轨生存能力,要求卫星具有高度的自主性,这也依赖于星务中心计算机的调度能力。因此,要求星务中心计算机功能强、能应付各种恶劣环境、并具有很强的自适应性,即能在线检测现场并自主实施决策处理。宇航计算机芯片是微小卫星整星电子系统一体化设计的一个重要的组成部分,由于一旦进入太空,空间计算机系统就具有不可修复性,这就要求系统有很强的容错能力,即使在故障条件下,还能正常工作。

系统总体方案

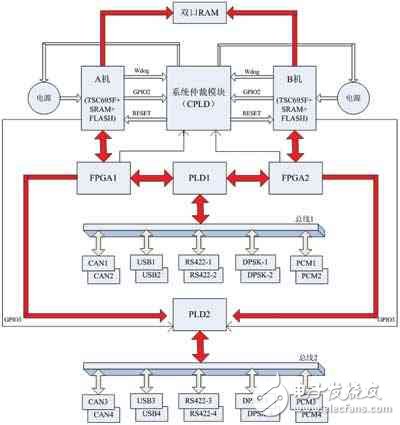

星务中心计算机采用模块级冗余技术来增强系统的可靠性,内部主要的电路模块均采取双冗余设计,如CPU模块(双TSC695F)、CAN总线模块、USB总线模块、遥测输出通道模块、遥控输入通道模块等。当前正在运行的电路模块发生故障时,系统通过容错电路自动切换或由地面控制切换到另一个备份的电路模块,继续当前电路模块的工作,而发生故障的电路模块则由地面根据其遥测状态数据判断其故障并采取相应的措施。CPU模块可采用双TSC695F抗辐照CPU,其工作频率最高可达50MHz,是一款比较适合航天领域应用的CPU,系统原理框图如图1所示。

图1 系统原理框图

从图1可以看出,A机和B机有各自的最小系统电路,即有独立的SRAM和Flash等,不会互相影响。同时,A机和B机共享外围IO设备,这是通过PLD1和PLD2来实现的。在PLD1和PLD2中,主要实现各功能IO外设总线的切换,因为所有IO外设的数据、地址以及控制总线都是由FPGA实现。这样,通过PLD1或PLD2,就可以把总线1和总线2上的IO外设挂在A机上运行或是挂在B机上运行了,从而实现功能部件的容错。而系统级的容错主要是靠系统仲裁模块来控制的,在这里的系统仲裁模块是采用高可靠性的宇航级PLD来实现的,该PLD要实现的功能相对简单,逻辑清楚,主要接收双机的看门狗信号和心跳信号,同时输出双机系统复位以及关双机电源信号的功能,从而实现双机系统自主容错功能。

本设计采用了由欧洲宇航局设计、法国TEMIC公司生产的专门应用于宇航工业的32位RISC抗辐照处理器芯片TSC695F。其特点包括:速度更高、功耗低于1.5W;抗辐照能力强;内置一个片上调试器(OCD),用于在软件开发和校验期间的非侵入程序执行控制;内部集成了内部/外部总线奇偶校验和外部总线EDAC纠错检错以支持容错功能。

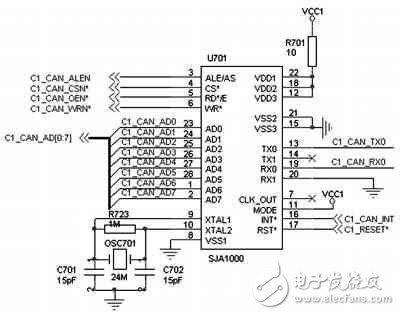

图2 CAN总线接口电路图

TSC695F的标准版本能够提供高达20MIPS的速度,具有抗单粒子干扰能力和超过300krad的总辐照剂量耐受力,能够满足我国卫星应用需求。

TSC695F是整个星务中心计算机控制系统的核心,控制系统所有的电路,以下分别介绍各功能电路模块的设计。

1 存储器接口

为了满足系统复杂的运算和数据存储要求,提供了两片512K×16位的SRAM,总计2MB,为运行RTEMS实时操作系统提供了丰富的存储资源。另外采用4MB Flash作为程序存储区。以上所有的存储器电路均带有EDAC功能,通过TSC695F自身的EDAC功能,对存储区的数据进行实时的数据错误检测和纠错。

2 CAN总线接口

CAN总线接口电路主要由CAN总线控制器、收发器和高速隔离光耦组成,CAN总线控制器采用的是SJA1000,是CAN总线接口电路的核心,主要完成CAN总线的通信协议,而CAN总线收发器的主要功能是增大通信距离,提高系统的瞬间抗干扰能力,保护总线,降低射频干扰(RFI),实现热防护等,访问CAN总线是通过TSC695F的I/O空间实现,地址逻辑译码由FPGA实现。CAN总线接口电路如图2所示。

3 USB总线接口

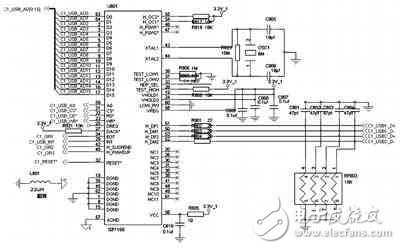

USB总线控制器采用ISP1160,该芯片支持USB 2.0协议,支持全速和低速两种速度模式,提供两个USB主下行端口,支持控制传输、中断传输、批量传输和同步传输四种传输模式,速度最高可达12Mb/s,访问USB总线的地址空间是通过访问TSC695F的IO空间实现的,地址的逻辑译码由FPGA实现。USB总线接口电路原理图如图3所示。

4 RS422总线接口

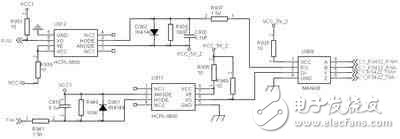

RS422总线接口电路由串口和RS422电平转换芯片构成,串口的功能由FPGA实现,带16B FIFO,波特率有115 200/38 400/9600多种选择;RS422总线电平转换芯片采用MAX488MJA,为了提高抗干扰能力,采用了隔离电源,电源的完全隔离可采用小功率电源隔离模块B0509LS-1W实现,虽然增加了节点的复杂程序,但是却提高了节点的稳定性和安全性。RS422总线接口电路原理如图4所示。

图3 USB总线接口电路图

容错电路设计

系统容错设计是整个系统设计的关键,容错电路要求简洁、可靠,容错措施包括以下几部分。

1 EDAC容错

利用TSC695F自身的EDAC功能,可以实现内存或总线的EDAC,从而达到对内存和总线的一位或两位错误的纠正和检测。

2 看门狗检测

系统仲裁检测电路中对由双TSC695F组成的主/备用机设置了“看门狗”监视器,系统正常工作时,会周期性地进行“喂狗”动作,当系统发生故障时,“喂狗”动作停止,产生系统复位,如果系统连续四次复位均不正常,则系统仲裁检测电路会进行系统切换操作,切断故障机电源,打开备用机电源。同时,运行故障检测定位程序,找出故障原因。

3 心跳信号检测

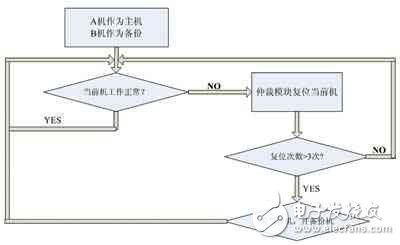

当主机在正常的运行过程当中,会周期性地通过GPIO口发出一系列的方波信号告知系统仲裁模块当前工作正常,当系统故障时,心跳信号消失,由仲裁模块进行复位操作,当5次复位均无效后,进行电源的切换,从而实现容错的目的。

4 双系统自主容错

本系统可以分为冷备用动态双模冗余模式和热备用动态双模冗余模式。

在冷备用动态双模冗余模式下,工作状态如下所述:系统默认A机为主机,B机为备份机,同时关闭B机电源,由两个开关信号GPIO2和GPIO3来控制PLD1和PLD2,PLD1和PLD2的功能主要是实现A/B机总线的开关切换,即选择A机的IO功能总线还是选择B机的IO功能总线,同一时刻只有一路总线有效,默认情况下PLD1工作,PLD2处于热备份状态。当PLD1控制下的IO功能模块出现故障时,产生出错中断,切断PLD1的开关,同时通知CPU切换到PLD2控制下的总线工作,如果PLD2控制下的IO模块也出现了故障,那么这时由FPGA1产生一个信号通知系统仲裁模块关闭A机的电源,打开B机的电源,从而实现双系统间的容错切换。

在热备用动态双模冗余模式下,工作状态如下所述:系统上电后,A机和B机都上电,A机为主模块,B机为从模块,A机B机同步工作,但B机不作系统输出,这样,当进行数据通信时,A机和B机可以对接收的数据进行数据比对。如果发现数据不同,则先由A机进行通道切换,再进行数据的通信,再进行数据比对。如果发现A机出现故障,则系统进行重构:先切除原主模块,再将原备用模块切换为主模块,同时通过读取双口RAM的数据作为最后一次传输的结果,保证数据不丢失。

图4 RS422总线接口电路图

图5 容错流程图

容错流程如图5如示。

软件开发平台

随着卫星技术的不断发展,以及实际应用需求的不断提高,星务计算机所要处理的任务越来越复杂,其运算量也随之变得越来越大,以往对底层硬件依赖程度较高的“控制流+中断”的程序结构已不能适应星务计算机的发展。为了解决这个问题,我们引入了嵌入式实时多任务操作系统(EOS)——RTEMS,利用珠海欧比特控制工程股份有限公司开发的基于此操作系统的Orbita EOS嵌入式操作系统及其Orbita EOS 开发工具,可大大提高软件编程效率和可靠性,具体可参考Orion4.0用户手册。

结束语

在采用双TSC695F作为容错星务计算机的研发过程中,深深感觉到容错功能的重要性,容错功能的优良与否直接影响到星务计算机在轨的生存能力,除了硬件上的容错外,软件方面的容错也不容忽视。

-

处理器

+关注

关注

68文章

19275浏览量

229761 -

计算机

+关注

关注

19文章

7492浏览量

87921 -

总线

+关注

关注

10文章

2879浏览量

88070

发布评论请先 登录

相关推荐

双TSC695F处理器在星务中心计算机系统中的应用分析

双TSC695F处理器在星务中心计算机系统中的应用分析

评论