本文阐述了一种芯片时钟与功耗管理控制器的工作原理,进行了模块划分,采用硬件描述语言实现了设计,并利用Synopsys公司的EDA工具进行了仿真和综合。该控制器已成功应用于东南大学ASIC中心研制的嵌入式处理器芯片Garfield4Plus中,并通过了实际的流片和测试。 在SoC芯片设计中,功耗是微处理器芯片是否成功的重要标准之一。同时,作为一个庞大的数字电路系统,处理器芯片的时钟架构及其控制也将变得尤为重要,将直接影响到芯片的功耗。基于以上考虑,整个芯片的时钟和功耗必须得到统一的管理和控制。包括核与总线在内的各功能模块的时钟应当能够跟据具体工作需要自由开关,以保证芯片尽可能地减小功耗。因此,处理器中需要一个专门的时钟与功耗管理控制器(以下统称PMC)来实现这些功能。PMC控制着整个芯片的工作模式和系统时钟频率,其稳定和完善将影响整个芯片的性能。

本文通过对PMC工作原理的分析确定了设计的总体结构并进行了具体的模块划分,使用基于硬件描述语言的逻辑综合方式进行了设计实现,并成功应用于东南大学ASIC工程中心研制的嵌入式处理器芯片Garfield4Plus中,通过了实际的流片和测试。

PMC功能描述

PMC负责管理整个芯片工作模式的切换和系统时钟频率的设定,并负责管理芯片上各功能模块的时钟信号和复位信号。通过设定PMC的功能寄存器,可以控制芯片在SLOW、NORMAL、IDLE、SLEEP四种工作模式间进行切换。

系统启动后默认工作在SLOW模式下,时钟频率较低,系统时钟由外部晶振直接提供,并且可以通过设置PMC相关控制寄存器,得到分频后更低速的时钟。

NORMAL模式是系统最常用的正常工作模式,系统工作在较高的频率上。外部晶振时钟通过DPLL数字锁相环倍频后,还可以再次被分频,得到一个可选频率范围较宽的高速时钟。数字锁相环倍频值和稳定时间等参数可以通过PMC进行设置。

当内核空闲时可以设置系统进入IDLE模式。当总线也空闲时,内核时钟将被关闭,同时停止对外部存储设备的操作,可以大大减小系统功耗。这种模式可以被各种内外部中断信号唤醒,唤醒后的系统将恢复到进入此状态之前的工作模式继续工作。

如果系统当前工作全部完成,整个系统都空闲的时候,可以设置系统进入SLEEP模式。PMC将会关闭除实时控制模块RTC以外的所有模块,系统功耗降低到最小。系统将会等待外部唤醒信号或RTC的定时唤醒信号来恢复系统时钟。被唤醒的系统将会首先进入SLOW模式。为了确保实现系统的唤醒,RTC和系统时钟唤醒模块使用独立的电源和晶振。

PMC还可以自由控制各功能模块时钟的开关。在正常的工作模式下,可以关闭暂时不用的模块以减小系统的功耗。另外,PMC还管理系统的复位信号并实现软件复位功能。

模块划分及实现

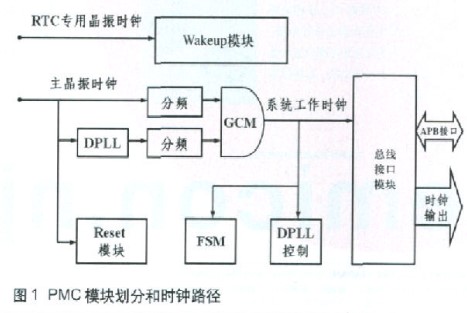

根据以上对于PMC工作原理和欲实现功能的分析,可将PMC划分为6个功能模块:PMC控制器状态机(FSM)、数字锁相环控制器(DPLL控制)、时钟分频选择模块(包括两个时钟分频器和一个无毛刺时钟切换专用电路GCM)、复位信号控制模块(Reset)、系统时钟唤醒模块(Wakeup)和总线接口模块,如图1所示。另外,数字锁相环DPLL为硬件宏模块,其性能经过专门的调试和验证以保证符合使用要求;GCM用于保证时钟切换时电路能够稳定工作。

从图1中还可以清晰看出PMC的时钟结构。Wakeup模块使用RTC的专用晶振时钟,以保证主时钟关闭后还能正常工作。Reset模块使用主晶振时钟。主晶振时钟经过可选分频得到较慢的时钟,同时主晶振时钟经过DPLL倍频,再经过可选分频得到较快的时钟。两路时钟经过GCM的平稳切换可获得整个系统所使用的工作时钟,该时钟将会分别提供给内核、总线和各功能模块(包括PMC自身的控制和接口模块)。

PMC控制器状态机

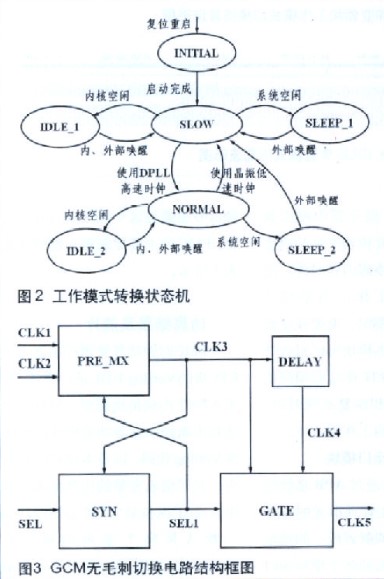

PMC控制器状态机的功能是决定系统的工作状态变化,并根据所处工作状态输出控制信号以及与其它模块的握手信号。此模块是整个PMC的控制核心,它可以分析软件命令,根据软件命令改变系统当前的工作模式,并收集总线、存储器、中断控制器等其他功能模块的工作状态信息;再根据这些信息控制工作模式的改变,输出包括开启晶振时钟、开启数字锁相环、时钟源选择、SDRAM自刷新等控制信号,以及与总线、中断控制器等模块的握手信号。系统工作模式转换的状态机如图2所示。

数字锁相环控制器

数字锁相环控制器负责根据PMC的相关控制寄存器配置数字锁相环DPLL,并通过硬件计数实现用户设定的稳定过渡时间,以保证DPLL有足够的稳定时间来锁定所设置的工作频率。控制器状态机发出的时钟选择命令和用户发出的频率重配命令都要经过此模块的管理,以保证切换过程中的时钟稳定。

时钟分频选择模块

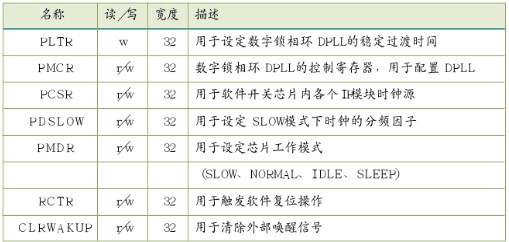

时钟分频选择模块负责选择和产生整个系统工作所需的时钟信号。时钟的可选范围和时钟切换的稳定,对于 PMC和整个芯片都十分重要。本文采用2MHz“5MHz的主晶振时钟和经过DPLL倍频后的100MHz”300MHz时钟作为时钟源,再经过多种倍率的可选分频,最终获得一个比较宽的可选时钟范围。为了提高时钟切换的稳定性,还专门设计了一种无毛刺时钟切换电路GCM(专利电路),可以在三个周期之内平稳切换两路各种周期差异的时钟,并同时改善输出时钟的质量。在本设计中,GCM用以实现晶振和DPLL两路时钟的平稳切换。

GCM的原理框图如图3所示。用普通二选一电路(PRE_MX)初步切换得到的时钟CLK3同步外界输入的时钟选择信号SEL;得到的同步选择信号SEL1实际控制时钟的切换,同时SEL1再经过进一步同步得到屏蔽残缺周期的门控信号;最后用门控信号去除时钟切换中的不稳定部分,得到平稳的时钟输出。

复位信号控制模块

复位信号控制模块负责接收外部复位信号和软件复位信号,并按照工作时序的需要,分别向芯片的各个功能模块发出复位信号。可以向某些对复位有特定时序和顺序要求的模块单独发送复位信号。并且可以区分软、硬件复位,对不同的模块集合进行复位。

系统时钟唤醒模块

系统时钟唤醒模块负责恢复关闭的系统时钟,并保证时钟稳定可用。在系统从节能模式(IDLE或SLEEP)恢复到正常工作模式(NORMAL或SLOW)的过程中,系统必须将已关闭的时钟恢复到正常稳定的状态。当系统从IDLE模式下唤醒时,需要恢复内核的时钟。本模块可以接收外部的唤醒信号形成一个唤醒中断,提交到中断控制器,这与其他所有模块产生的内部中断一样,可以唤醒内核时钟,使系统恢复正常工作。当系统从SLEEP模式下唤醒时,需要恢复整个系统的时钟。本模块可以接收外部唤醒信号或者RTC的定时唤醒信号,并稳定开启和恢复系统时钟,最终切换到正常的工作模式下。

AMBA总线接口模块

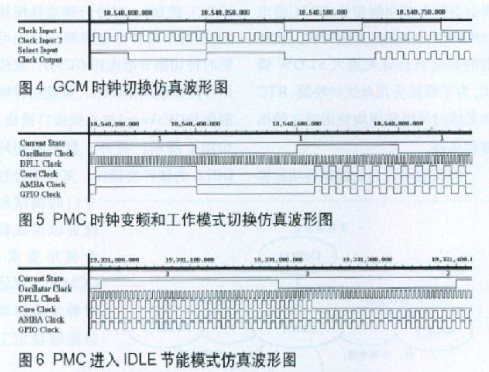

RISC的内核通过APB总线读写PMC时钟功耗管理单元的寄存器,这些寄存器映射到统一的地址空间。另外,输出到各个模块的时钟信号也通过这个模块进行开关控制。PMC的主要控制寄存器描述如表1所示。

仿真结果及流片

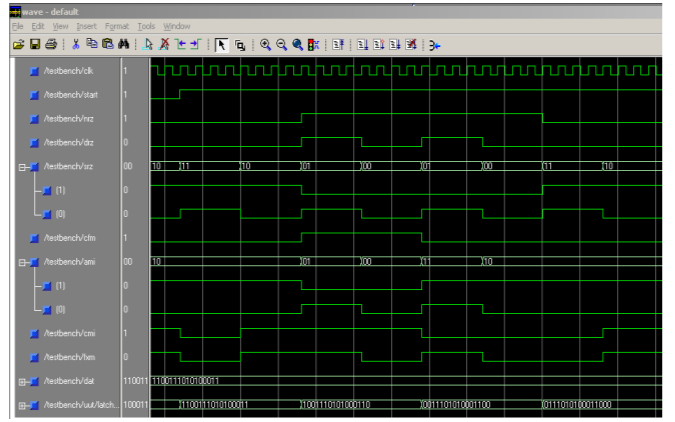

PMC时钟功耗管理控制器采用RTL级的Verilog HDL进行描述。使用A720T内核仿真模型、AMBA总线和中断控制器等功能模块的RTL级Verilog代码,以及本设计的源代码,共同组成完整的仿真环境。其中A720T内核是ARM公司设计的一款ARM7系列内核,在ARM7TDMI基础上增加了虚拟地址与物理地址转换器MMU、指令Cache和数据Cache。A720T内核仿真模型是ARM公司提供给授权开发机构用以完成仿真的功能模型,它不能被综合,只能用于功能验证。使用Synopsys公司的EDA工具VCS对本设计的功能进行仿真和验证。其中GCM模块还使用HSIM进行了SPICE晶体管级的模型仿真。GCM时钟切换的仿真结果如图4所示,PMC时钟变频和工作模式切换的仿真结果如图5所示,PMC进入IDLE节能模式的仿真波形如图6所示。从仿真结果可以看出,PMC能够正常完成预计功能,可以稳定地改变时钟频率,并根据工作模式开关时钟。

PMC时钟功耗管理控制器已成功应用于东南大学ASIC工程中心自主开发的基于ARM7的嵌入式处理器Garfield4Plus中。通过该芯片的实际流片,PMC获得实片测试的机会。测试结果表明,PMC能够正常稳定地完成预计功能,包括工作频率的实时配置、工作模式的切换以及芯片的节能和唤醒。

结语

本文描述的PMC设计的特点在于工作时钟的统一和时钟结构的清晰简洁。GCM无毛刺时钟切换电路,使得多个时钟源(包括每个时钟源的各种不同的频率配置)在真正提供给系统使用之前就得到了很好的统一。这种时钟结构可以带来更好的系统稳定性和时序上的余量,也就代表着可以使用更高的系统时钟频率。

今后对PMC的优化应当重点关注以下两点。一方面,应当使PMC在针对不同系统的具体特点时,能够对功耗的实时管理进行更灵活的配置。既要保证最大限度的节能,又要增加PMC本身的可移植性。另一方面,应当进一步探索更科学的结构,使提供给系统的时钟在更灵活的配置方式下,仍然能够保证安全和稳定。

-

芯片

+关注

关注

459文章

51669浏览量

430533 -

控制器

+关注

关注

113文章

16624浏览量

180665 -

soc

+关注

关注

38文章

4260浏览量

220175

发布评论请先 登录

相关推荐

VHDL语言实现DDR2 SDRAM控制

基于Verilog硬件描述语言的IEEE标准硬件描述语言资料合集免费下载

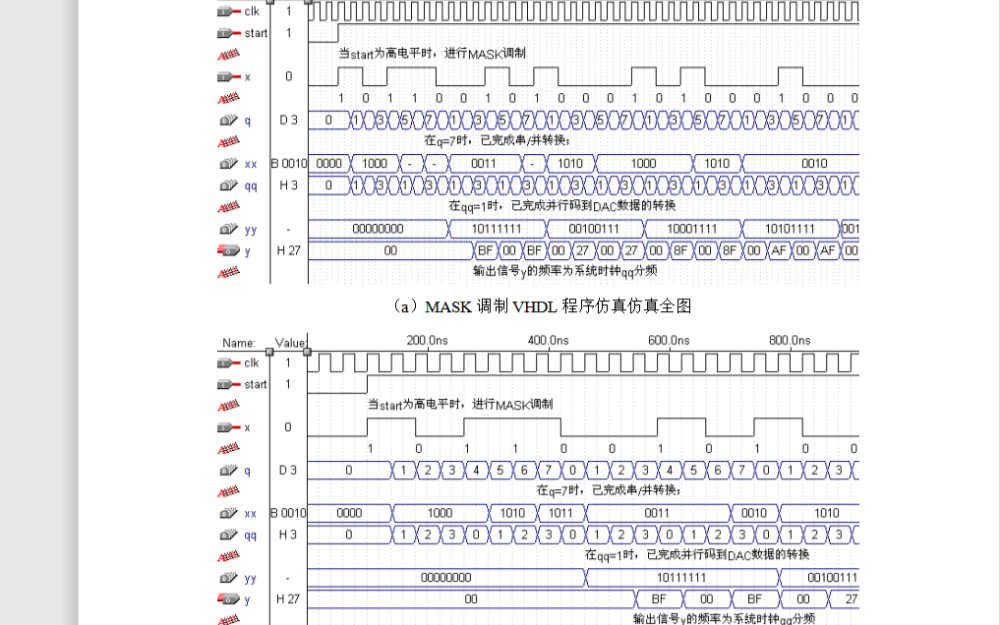

使用VHDL硬件描述语言实现基带信号的MASK调制的程序与仿真

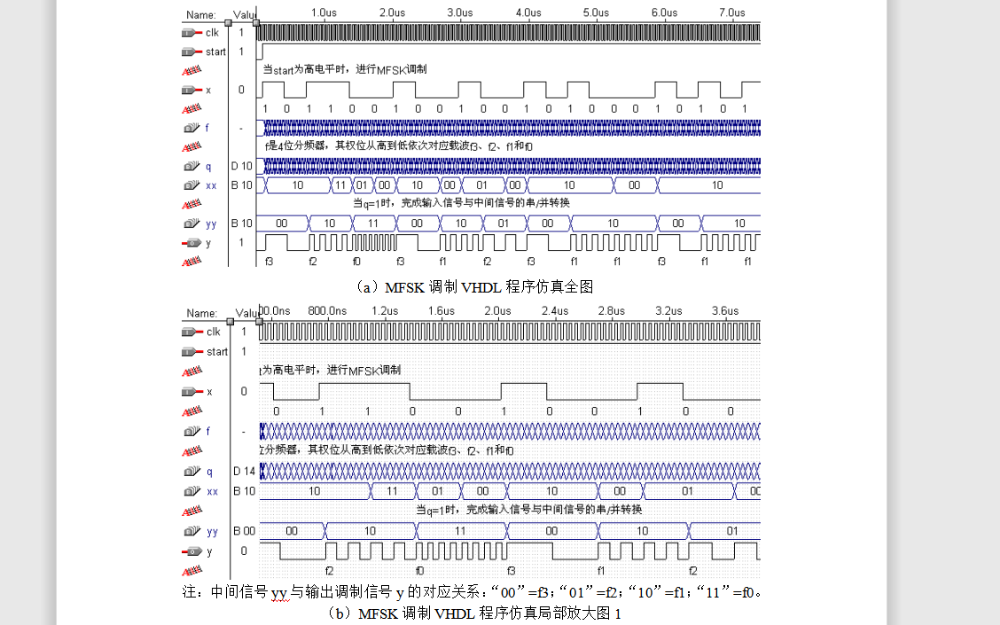

使用VHDL硬件描述语言实现基带信号的MFSK调制的程序与仿真

采用硬件描述语言实现PMC时钟功耗管理控制器的设计

采用硬件描述语言实现PMC时钟功耗管理控制器的设计

评论