高速串行技术的不断发展,使得信号从发射机传送到接收机时,均会经过复杂的交互,最终发生严重的高频损耗。

全新的测试要求

计算机、消费电子和通信行业设计核心正采用最新的高速串行技术,数据传送速率持续提高,如10Gb/s以太网的出现、PCI Express已经从1.0版演进到2.0版,速率也从2.5Gb/s提高到5.0Gb/s、即将出现的8Gb/s PCIe Gen3和6Gb/s SATA III……高速串行技术的不断发展,使得信号从发射机传送到接收机时,均会经过复杂的交互,最终发生严重的高频损耗。这样,对串行数据的测试也必将面临前所未有的挑战:数据速率远远高出原有技术;信号完整性在整个链路中至关重要;需要提供复杂的分析和互通测量;大多数高速串行技术采用多路结构,需要检定每条通路。

传统的测试方法是:分开检定和测试各个子系统;留出充足的设计余量,保证系统可靠运行;进行标准的一致性测试,保证互通能力。这些措施可以满足速度较低的设计需求。对高速串行数据而言,传统测量技术远不能适应现有的设计要求。

解决方案

● 电源管理和跨总线分析

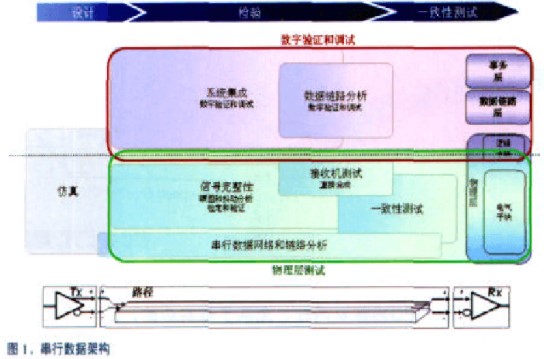

串行数据是三层架构(如图1),分为物理层(电气子块和逻辑子块)、数据链路层和事务层。物理层的逻辑子块是负责进行链路宽度、初始化和速度协商的;数据链路层是保证发送到链路上的数据的正确性以及数据在链路上被可靠地分组传送;事务层是进行建立请求/结束交易、分组流量控制和信息传送的。只有全面了解系统,才可以查找系统中其它总线衍生出的难检问题。

以业内广泛推广的串行数据标准之一的PCI Express (PCIe)为例,产品已经从PCIe 1.0演进到PCIe 2.0,速度也从2.5Gb/s提高到5.0Gb/s。已有的协议分析仪可进行PCIe 2.0协议信息及跨总线分析,然而PCIe 2.0最大的验证挑战来自于电源管理。

对于电源管理,它需要动态协商使用的通路数量或“链路宽度”(最多16路)、链路速度(2.5Gb/s “ 5.0Gb/s)和空闲状态,才可以尽量的节约能耗。电源管理在系统中举足轻重,这样笔记本电脑才可以延长电池工作时间,服务器系统才能够节约能量。验证物理层事件的能力是至关重要的。

泰克公司新推出的TLA7S08和TLA7S16串行分析仪除了具有协议信息及跨总线分析功能,与众不同之处是它的电源管理功能。它可以分别采集x1、x4链路或x8链路,两块TLA7S16串行分析仪模块可用于双向x16链路。PCIe 2.0链路可以动态改变宽度(通路数量)。例如,8路链路(x8)可以变成4路(x4),后者要求的能耗较低;在系统需要时可以返回x8。PCIe 2.0规范还允许链路在2.5Gb/s ” 5Gb/s之间动态交替速度,同时支持PCIe 1.0和2.0标准。此外,在不使用时,链路可以在短时间内进入空闲电源状态。在宽度和速度变化期间及在电源管理状态转换期间验证这些链路正常运行非常重要。泰克的串行分析仪以独一无二的方式验证和调试这些链路流程的运行情况。

● 串行数据链路分析

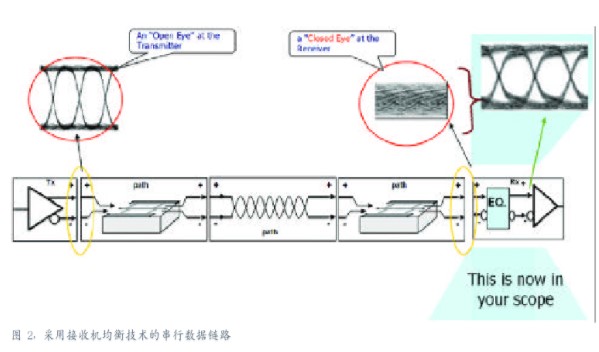

在物理层,当信号通过信道(如:电缆、PCB背板等)时,因信道损耗和其它失真改变了接收机上的NRZ数据信号形状,把所需的方波变成严重失真的闭合眼图波形,如图2所示。如果采用传统的测试方法将会得出系统无法运行的结论,但事实上链路依然运行良好。究其原因是系统中采用了接收机均衡器。均衡器使眼图张开(如图2中蓝色部分),允许区分逻辑状态高和逻辑状态低。

接收机均衡通常采用两种均衡技术,即FFE前馈均衡和DFE判决反馈均衡。FFE可以提升频率、补偿数据传输衰减最严重的频谱部分,同时也极大地放大了噪声。DFE是更加先进的均衡方法,它是一种基于干净(无噪声)比较器输出中的反馈的电平提升,因此不会注入噪声。

串行数据链路分析主要是进行信号完整性和一致性测试,具体是指从发射机、信道、抖动噪声、BER和链路等角度分析产品性能。传统的发射机+信道组合显然是不够的。泰克DSA8200数字串行分析仪通过iConnect软件实现TDR/TDT和S参数测试,提供信道检定功能。运行在DSA8200上的80SJNB Advanced软件,拥有完整的均衡和信道仿真功能。在接收机一侧提供重要的FFE和DFE均衡方法,在发射机一侧支持生成和测量预加重和去加重信号;通过信道仿真,工程师可以采集发射机输出上的信号。借助仿真的信道使信号失真,然后检验信道最终的性能,无需提供物理硬件;扩频时钟(SSC) 广泛用于台式计算机和笔记本电脑中,SATA和PCI-Express等标准中都采用了SSC。80SJNB Advanced软件支持SSC信号采集和分析,可以对高级发射机检定。

经验借鉴

● 提供完整的综合解决方案

串行数据分析领域需要完整的 综合解决方案,包括实时示波器、采样示波器、任意波形发生器、串行分析仪和完整的测试软件;在对数据链路层和事务层进行逻辑分析时,从用户实际需求出发,增加对物理层事件的验证;跟随行业和标准的发展,提供针对性的解决方案,以缩短被测产品的研制周期。泰克公司逻辑分析仪产品规划师Sarah Boen女士表示:“泰克公司提供了高速串行数据分析整体解决方案,工程师可以从发射机到接收机检定和测试整个设计的标准一致性。”

-

电源管理

+关注

关注

115文章

6183浏览量

144533 -

计算机

+关注

关注

19文章

7500浏览量

88028 -

总线

+关注

关注

10文章

2887浏览量

88117

发布评论请先 登录

相关推荐

多FPGA系统中自定义高速串行数据接口设计

怎么实现基于FPGA的具有流量控制机制的高速串行数据传输系统设计?

高速串行总线技术发展与应用分析

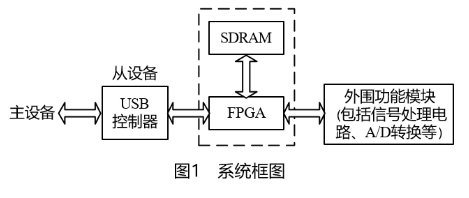

采用通用串行总线USB技术的高速数据采集卡的设计方案

高速串行数据技术的电源管理和跨总线分析

高速串行数据技术的电源管理和跨总线分析

评论