为了满足现代通信系统对传输速率和带宽提出的新要求。人们不断地推出一些新的数字调制解调技术。正交幅度调制解调(quadrature ampli-tude modulation and demodulation)就是一种高效的数字调制解调方式。与其它调制技术相比,这种调制解调技术能充分利用带宽,且具有抗噪声能力强等优点。因而在中、大容量数字微波通信系统、有线电视网络高速数据传输、卫星通信等领域得到广泛应用。

1 16QAM调制原理

一般情况下,正交振幅调制的表达式为:

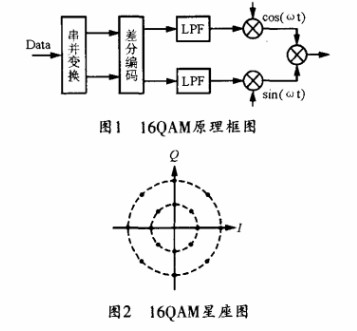

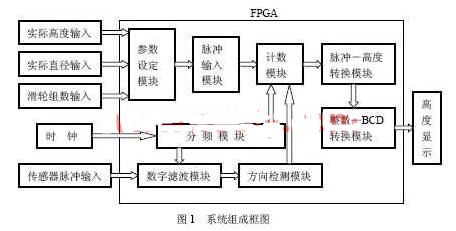

式中,A是固定振幅,(dm,cm)可由输入信号确定。(dm,cm)则可决定已调QAM信号在信号空间中的坐标点。16QAM正交振幅调制系统组成框图如图1所示。基带信号经过串并变换后转化为IQ两路并行数据流,该并行数据流的宽度为4 bit,其中高位的1 bit映射到内外圆,低位的3bit映射到内(外)圆上,这样就形成如图2所示的星型星座图。差分编码后的数据经过成型滤波器后和相互正交的正弦或余弦载波进行调制,被调制后的IQ路正交信号再进行矢量相加,即可形成调制信号输出。

2 16QAM调制器的FPGA实现

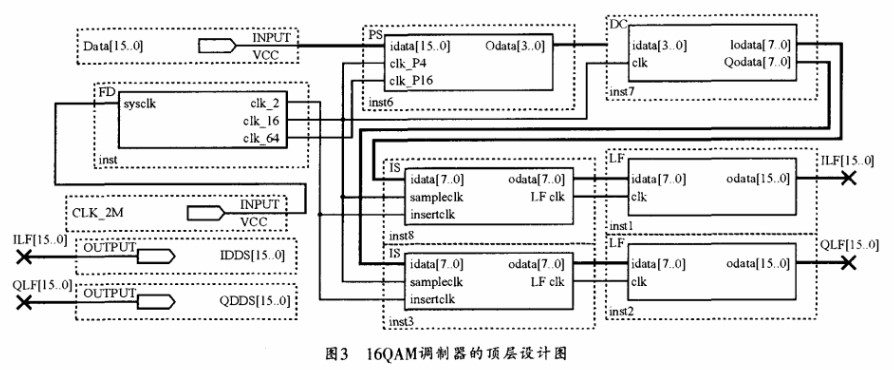

16QAM调制器可在ALTERA公司的CYCLONE系列芯片EPlC6Q240C8上实现,EDA工具是与之配套的QUARTUS II 4.2软件。在设计中,底层设计可使用Verilog HDL语言来实现,顶层设计则采用原理图方式实现,其顶层设计图如图3所示。

2.1 时钟分频模块

时钟分频模块FD利用N分频器对2 MHz系统时钟信号进行N分频,以产生调制器模块所需的工作时钟。N分频器是由模N/2计数器实现的,分频输出信号模N/2可自动取反,以产生占空比为1:1的时钟信号。由于信号源产生的基带信号为16bit并行数据,其速率为32 kbps,经并串转换后的4 bit并行数据速率为128 kbps,所以,本设计还采用了16分频器和64分频器。同时还设计了2分频器,三个分频器可分别产生1 MHz时钟、128kHz时钟和32 kHz时钟。

2.2 并串转换模块

并串转换模块PS可通过4级锁位寄存器来实现。并行16位的输入数据按照并行4位的格式串行输入到差分编码模块。

2.3 差分编码模块

差分编码模块DC在调制器中的作用是通过编码和信号映射把二进制比特数据转换为具有幅度和相位特性的数据,然后把这些数据送到后面的模块中进行调制。

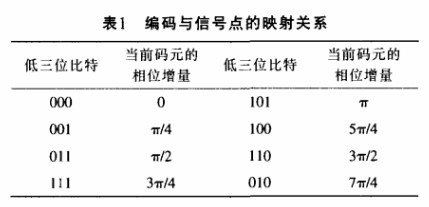

根据星型16-QAM星座图的特点,这里规定每个码元由四个比特组成。其差分编码规则是:每个码元的第一个比特通过差分方式来改变QAM相量(即图1中从坐标原点指向每个信号的矢量)的振幅。如输人的该比特为“1”,则将当前码元的相量振幅改变到与前一个码元的相量振幅不相同的振幅环上。若输入的该比特为“0”,则使当前码元的相量振幅与前一码元相同。每个码元中的其余三个比特则通过Gray差分相位编码的方法来改变信号的相位。也就是说,通过Gray编码来改变当前码元信号相量与前一码元信号相量的相位差(即相对相位)。这些比特数据与相位差的关系如表1所列。

根据上述规则,即可通过对第一个比特的编码来得到码元的振幅(Ai,i=1,2),而通过对剩余三个比特的编码则可得到当前码元的相对相位。把前一码元的绝对相位加上当前码元的相对相位,就可以得到当前码元的绝对相位(θi,i=0,1…7)。这样,就可以得到第k个码元经过差分编码后的输出脉冲值Aiejθi(I路的输出值为,Aicos(θi)Q支路的输出值Aisin(θi))。

在FPGA实现差分编码的模块中,比特数据经过编码可得到振幅值和相位值。然后利用上述两个值作为地址,并通过查ROM表的方法就可得到输出脉冲值。因为与直接法相比,用查表法进行设计不涉及正余弦运算,也不需要进行乘法运算,因而程序执行速度快。同时,由于需要存储的脉冲值只有16种,所以不会占用FPGA太多的资源。

2.4 内插模块

差分编码模块的输出数据速率是128 kbps,而在实现DDS的器件AD9857中设定的输人数据速率是1Mbps,为了使两者速率匹配,设计时可采用内插方法来实现。

内插模块IS的设计可采用最简单的实现方法,即在数据之问插零。零的个数N由内插前后数据的速率决定,本设计中N=7。内插模块可通过数据锁存器和计数器来实现。

2.5 成型滤波模块

内插模块IS的设计采用“插零”处理会导致码间干扰和带外辐射增大。为了减小其对信号解凋的影响,设计中应加入成型滤波模块。

在该模块设计中,滤波器的抽头系数可根据滤波器的冲击响应公式并通过Matlab仿真求得。仿真参数设定为:滚降因子α=0.35,滤波器长度N=51,一个符号周期内点的个数M=8。滤波器的实现可采用并行结构,每阶都有自己的乘法器,用于接收输入数据,并将其与抽头系数相乘。

2.6 载波正交变换

本设计中,16-QAM调制器中的载波正交变换并不是在FPGA中实现的,而是采用数字上变频器代替。这是因为调制系统的中频载波为36.864 MHz,经过内插滤波后,该输出信号频率可达百兆赫兹以上,这样的频率会使FPGA无法稳定工作。为此,本设计采用了专用DDS芯片AD9857来保证FPGA能够正常稳定的工作。

3 硬件测试

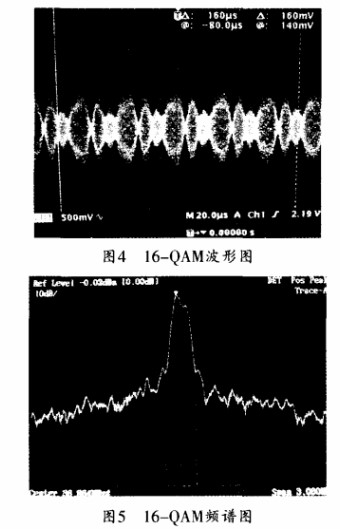

本没计的测试结果如图4和图5所示。从图4可看出:在系统码元之间,相位跳变分明,所得到的波形就是实际的调制波形。图5为信号频谱图,纵坐标每格10 dB,横坐标每格300 kHz,信号带外衰减大于30 dB。由图5可知,该系统的带宽大约为200 kHz,能完全满足预期设计要求。

4 结束语

多进制正交振幅调制由于具有很高的频谱利用率,而被广泛应用在中、大容量数字微波通信系统的载波键控方式之中。特别是当MQAM在未来4G移动通信采样以OFDM为主导技术的基带调制中,它将成为实现大容量的重要调制技术。本文利用EDA技术来实现16QAM调制器的设计是现代数字通信与EDA技术相结合的一个典型应用,这种电子设计的自动化方法也必将在数字通信领域得到广泛的应用。

-

FPGA

+关注

关注

1634文章

21831浏览量

608058 -

芯片

+关注

关注

458文章

51529浏览量

429508 -

vhdl

+关注

关注

30文章

819浏览量

128694

发布评论请先 登录

相关推荐

基于EP1C6Q240C8的FPGA芯片实现电子测试系统的设计

通信工程信号调制程序(16QAM)看不明白 ,求解答

基于FPGA的QAM调制器系统实现

基于VHDL的4PSK调制器的设计

基于FPGA的高阶QAM调制器的实现

基于SIMULINK的16QAM基带调制系统性能仿真

通过VHDL语言和EPlC6Q240C8芯片实现16QAM调制器的设计

通过VHDL语言和EPlC6Q240C8芯片实现16QAM调制器的设计

评论