自最初开始设计 PCB 以来,约束一直是定义成品物理电路板所必要的元素。尺寸和铜重量是最早的约束。而现在,高速的设计对电子设备的诸多参数有约束要求,尤其是差分对。

定义约束的目的在于尽可能多地消除错误来源,即消除那些需要设计返工的错误。而且,设计错误发现得越晚,返工成本就会越高。理想状况下,“设计即正确”的方法可使约束得到严格遵守,从而在设计过程中消除错误的可能性。但事实上,尽早验证信号完整性对确保满足所有约束至关重要。

设计不佳的用户界面往往是令约束设置既繁琐又耗时的原因之一。必须打开多个窗口,而且无法一次看到所有约束,这种设置方式往往令人晕头转向,极易出错,而且迫使用户一次只能手动更新一项约束。

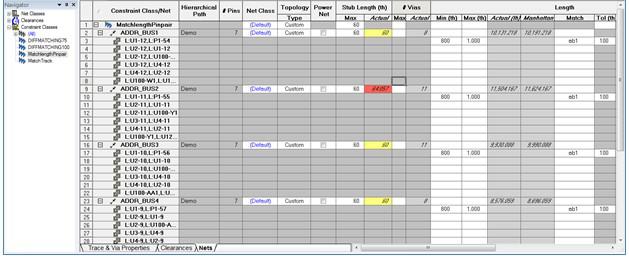

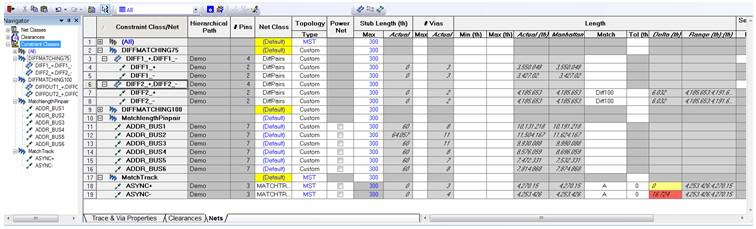

更多如Mentor Graphics PADS 产品等更为现代化的设计工具,均使用基于电子表格的方法简化了导入和评审约束的操作,相比基于对话框的传统方法具有明显的优势。

图 1:约束管理可能非常复杂,尤其在使用基于对话框的传统环境时。PADS 所使用的基于电子表格的方法简化了整个过程

利用强大的电子表格编辑功能(例如,多行/多列复制/粘贴和自动填充),可以快速导入或修改大量约束值。通过打开 PADS Constraint Manager 的两个实例,允许将约束值从一个项目复制到另一个项目,从而提供约束复用功能。

约束规范

一个特定的设计项目可能包含多个有用或无用的约束。常用的设计约束如下:

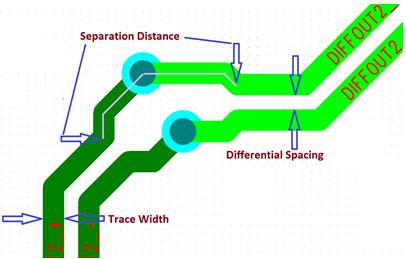

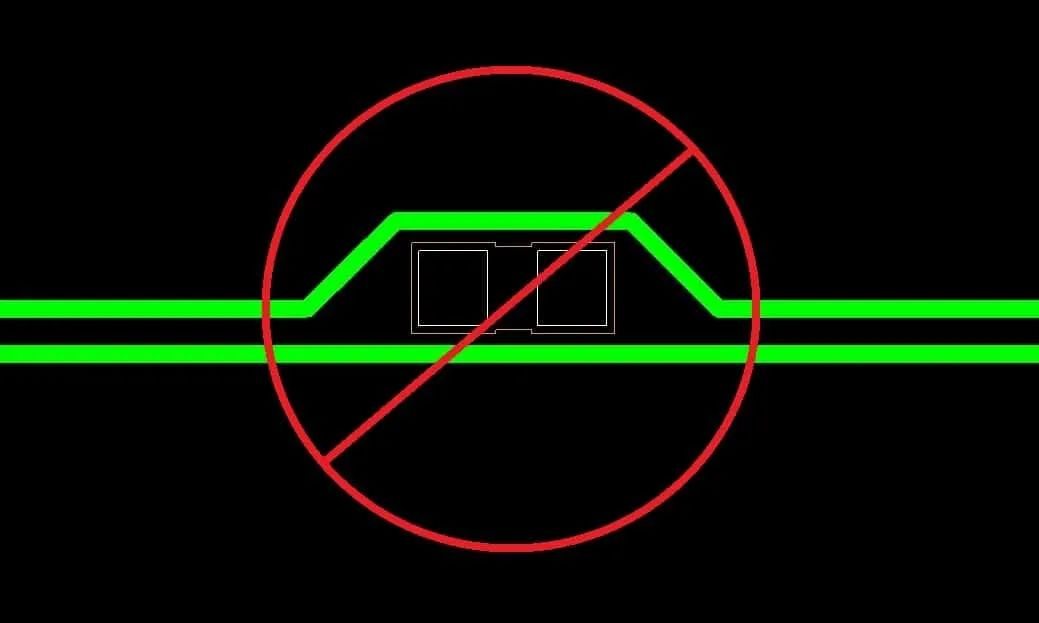

A.差分对约束包括:走线宽度、差分间距和最大分隔距离。最大分隔距离是一项层相关的约束,指定了走线在违反差分间距值的情况下能够并行布线的长度。

图 2:差分对约束

B.拓扑约束限制特定网络的布线模式。它们用于控制布线结构以及对网络分支(管脚对)施加长度限制。拓扑类型和最大支线长度是两类常见约束。拓扑类型可以不针对布线设置任何限制,或者以规定的方式限制布线。

最大支线长度约束应用于使用受约束的拓扑的网络类型。它限制了由邻近网络分支共用的走线长度。两项约束均可在约束类级别指定,或在单独的网络上加以覆盖。

C.长度约束针对网络和网络分支的布线长度施加限制,包括最小长度、最大长度和匹配长度。最小和最大长度约束可分配给约束类、单独的网络或单独的网络分支(管脚对)。

要定义差分对的匹配长度约束,需要使用匹配长度组。此方法针对组成员的相对长度设定限制,即任意两个组成员之间的长度差不得超过指定的容差值。匹配长度组可能包含网络或网络分支(管脚对)。不允许在一个组内混合网络和管脚对。

D.布线约束针对布线层、过孔使用和走线宽度施加限制。布线约束在网络类级别定义,并应用于网络类中的所有网络。它们对布线层的使用、布线允许的过孔类型以及允许的走线宽度范围施加限制。

图 3:此份关于 Mentor Graphics PADS Standard 的样例电子表格视图显示了可为具有自定义拓扑的单独网络分支指定的约束类型。此处显示了匹配长度限制和支线长度违规

E.间距约束定义了特定布线层上两个布线对象(例如走线、焊盘和铜皮区域)边缘之间允许的最小间距。

F.电源网络约束——诸如 PADS 之类的工具会基于预定义的标准名称(例如 GND、VCC、+5V、-12V 等)自动识别电源网络。

按类分组

在设计流程的早期阶段对网络类和约束类进行正确的分组和定义,可显著简化约束的定义和管理。分组约束可提高 PCB 设计效率,缩短设计时间,以及最终节省 PCB 设计成本。

差分对是由实施差分信号的两个物理网络构成的组。随着差分对数量的增加,一次定义一个差分对的做法变得极为繁琐。而自动化可快速、轻松地创建差分对。网络名称通常遵循模式名称。使用这些模式查找您想要分配为差分对的网络名称。随即显示建议的差分对列表;取消选中您不想分配的匹配项。

对于差分对,可以定义层相关的差分对间距。网络类用于组织和加快具有类似特征的网络的布线约束定义。对于网络类,您可以定义允许布线的层、这些层对应的走线宽度范围,以及网络类中的网络所允许的过孔类型。

约束类用于组织和加快具有类似电气和时序属性的网络的长度、拓扑和其他约束定义。尽管分配给约束类的约束会自动应用于类中的所有网络,但也可以为单独的网络、管脚对和差分对自定义特殊的约束值。

图 4:利用 PADS 的约束类,无需为单独的网络创建长度和拓扑约束

违规

传统上,约束违规是在您的 PCB 设计工具中执行检查和评审。PADS 工具支持在 PCB 设计环境或在约束管理环境内查看约束违规。通过在定义约束的环境内查看违规,工程师和设计人员可采用类似的方法访问此过程,这对工作流而言也更为自然。

查看并分析违规可使工程师在发现违规后即刻做出纠正。这是至关重要的一步,因为随着设计的进一步执行,修复问题所花费的成本会变得更高。通过在设计工具内查看违规,错误可在最短的时间内以最低的成本得到修复。

总结

约束管理应专为满足设计人员的日常工作过程需求而设计,具有直观、快速和简易的特点。采用统一的方法可确保实现“设计即正确”方法,并且消除在原理图与 PCB 设计环境中使用单独的约束管理工具所造成的错误。整个流程期间所有约束应同步并可访问。Mentor Graphics PADS 是约束驱动型 PCB 设计的理想工具。

-

pcb

+关注

关注

4329文章

23192浏览量

400671 -

电路板

+关注

关注

140文章

5006浏览量

99187 -

PADS

+关注

关注

80文章

808浏览量

108009

发布评论请先 登录

相关推荐

约束驱动型PCB设计工具简化差分对布线

约束驱动型PCB设计工具简化差分对布线

评论