1 引言

高速数据采集系统目前已在雷达、声纳、图像处理、语音识别、通信、瞬态信号测试等领域得到广泛应用。它的关键技术是高速ADC技术、数据存储与传输技术和抗干扰技术。当大量的高速实时数据经过模数转换后,必须高速存储,多通道高采样率的数据采集系统会产生巨大的数据流。这样就需要高速大容量的存储板将数据存储起来,然后再读回计算机进行处理。基于以上原因,本文设计了可以同时存储两通道采样数据的大容量存储板,板中采用了64片Samsung公司的高速大容量存储器K9F2G08UOM,使整块板卡的存储容量达到128Gbit。采用FPGA作为控制器,通过标准的CPCI工控机箱操作存储板,并通过CPCI总线将存储板上的数据高速读回计算机,提高了读取数据的速度。

2 K9F2G08UOM简介

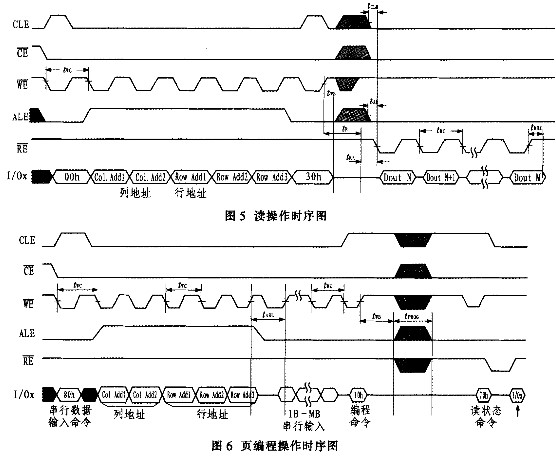

NOR Flash和NAND Flash是目前市场上的两种主要的非易失性闪存技术,本设计的目的是为了高速存储大容量的数据,因此,选择NAND型K9F2G08U0M存储器。它的存储容量是2 Gbit,8位位宽,页大小为2 048×8 bit,每块由64页组成,共有2 048块。每页带有64×8 bit的空闲存储区,共有8 192 K×8 bit的空闲存储区。页编程的典型时间为300μs,最大页编程时间为700μ8。页内连续最小访问时间为30 ns/Byte,即数据写入Flash数据寄存器的速度可达33 MB/s。但是单页数据的典型编程速度为2 048/300μs=6.8 MB/s,最慢的编程速度为2 048/700μs=2.9 MB/s。块擦除的典型时间为2 ms。K9F2G08U0M具有硬件数据保护功能,即在电源上电、掉电期间关闭编程/擦除操作。K9F2G08U0M内部写控制器使得所有的编程和擦除操作自动进行,片内包含一个页(2 048+64字节)的数据寄存器,读写过程中始终是将存储单元数据或外部数据先缓存到数据寄存器,然后再读出数据或写入存储单元。因此,它是基于页读写,基于块擦除的。当然,它也支持随机读写。但本设计目的是高速存储数据,因此对它的读写操作完全是基于页的。K9F2G08U0M的主要引脚有CLE(命令锁存允许)、ALE(地址锁存允许)、CE(片选)、WE(写允许)、RE(读允许)、WP(写保护)、R/B(准备好/忙)、PRE(上电读使能)、I/O0~I/O7(输入,输出)。其中I/O0~I/O7既可作为数据输入输出引脚,又可作为命令地址的输入引脚,命令、地址、数据分时复用,根据不同的命令区分地址和数据。一般的操作流程为:

1) 写入命令,通知器件所要完成的操作(读、写、擦除等);

2) 写入地址,即写入要读写数据的起始地址,包括列地址和页地址;

3) 如果是读或者擦除,写入一个确认命令。如果是写操作,输人待编程的数据,完成后输入编程确认命令。

因为K9F2G08U0M共有128 K页,每页的大小为(2 048+64)×8 bit,所以在写入地址时列地址需要12根地址线,页地址需要17根地址线。这样就需要5个时钟周期来写入地址。前两个时钟写入列地址,后三个时钟写人页地址。

3 系统设计

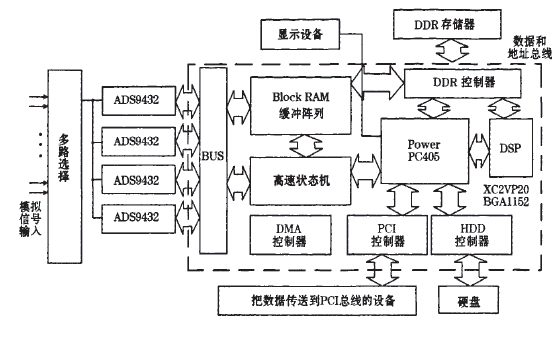

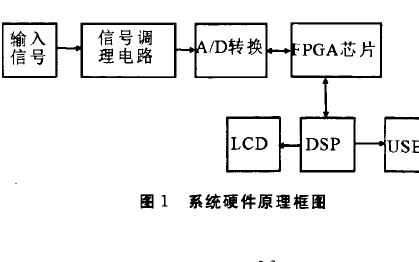

3.1 总体硬件设计

外部数据采集系统是2个40 MHz采样的16位A/D通道,所以设计时分成两个通道独立设计。虽然K9F2G08U0M的数据寄存器写入速度可达33MB/s,但在FPGA设计时,为了在时序上更加可靠,选择使用25 MHz的时钟设计,则K9F2G08U0M的写入速度为50 MB/s(把两个K9F2G08U0M并成16bit,写入速度即为25 M×l6 b/s)。这样,在FPGA内部开辟3个页大小的双口RAM作为缓存区就能满足40 M×16 b/s的写入速度,即在写第2、3个RAM的时间(25 ns×2 048×2=102.4μs)内,启动第1个RAM把数据写入Flash的数据寄存器,所需时间为40 ns×2 048=81.92μs,小于102.4μs。

在读回数据时,如以20 MHz读取Flash,以40MHz读出缓冲区中的数据,3个双口RAM就能刚好满足要求,如图1。读取K9F2G08U0M一页数据能达到33 MHz的速度,为了让读写Flash使用同一时钟,读Flash也采用25 MHz的速度。同时为了增加系统设计的冗余,采用4页的双口RAM作为缓冲区。所以每片FPGA内部至少需要4×2 048×16 bit=131 072 bit的存储空间。

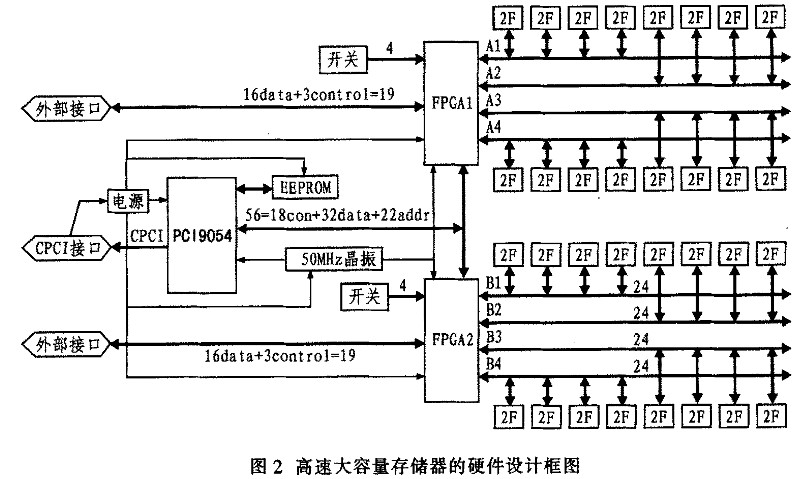

由于数据在写入Flash后还有较长的编程时间,一页的编程时间典型值为300μs,最大值为700μs。数据在存储上不能有任何的停顿,否则就会丢失数据,所以不能使用R/B信号进行设计。为了系统更加可靠,选择最大编程时间700μs。两次对同一组Flash进行写操作的时间间隔为700μs+81.92μs=781.92μs,一页的数据写到双口RAM要用25ns×2 048=51.2μs。总时间除以写一页数据的时间:781.92/51.2=15.3μs,说明一个循环内至少需要16组Flash才能满足要求。所以在设计中,对于每路A/D采样通道都用一片FPGA作为缓冲和控制系统,在每片FPGA内部都采用4个缓冲区,每个缓冲区对应一条外部总线,每条总线上挂有4组K9F2G08U0M×2(将两片Flash并成16位操作,即把I/O并成16位,共用控制信号线)。系统整体框图如图2所示。

图2中2个外部接口连接2个A/D通道,采用两片FPGA作为控制和缓冲区,每片控制16组Flash。存储板通过PCI9054与CPCI总线相连,通过CPCI总线可以将存储板数据高速读回计算机。

3.2 系统设计思想

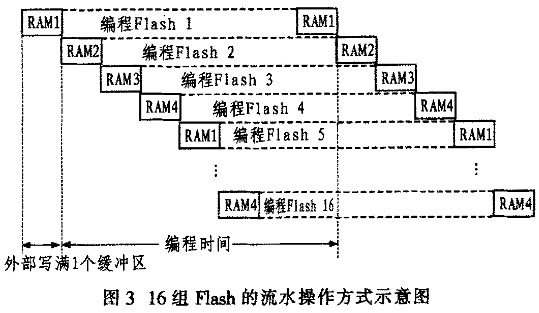

为了解决高速的数据采集和低速的Flash访问速度之间的矛盾,采取将数据流串并转换,复制多个操作模块并行处理的设计方法。通过利用FPGA内部的存储区实现4个双口RAM作为缓冲区。每条外部Flash总线用一个双口RAM,采集到的数据分时加载到4个RAM中,然后再写入Flash。写入Flash的操作以流水方式进行,具体方式如图3所示。首先,外部A/D采样通道写数据到RAM1。当RAM1写满时,加载数据到第一组Flash数据寄存器,加载完成后第一组Flash进入自动编程阶段;当RAM2写满时,第2组Flash加载开始,数据加载完成后,进入自动编程阶段。依次加载RAM3,当RAM4写满,第4组Flash开始加载后,FPGA内部控制重新写RAM1,开始对第5组Flash操作,然后依此循环方式对第6~16组Flash进行操作;当第16组数据加载完成后,第1组Flash已经编程结束,接着从第1组Flash开始加载和编程。可看出向16组Flash写入数据是并行的,通过并行写操作,可存储高速采集的数据。

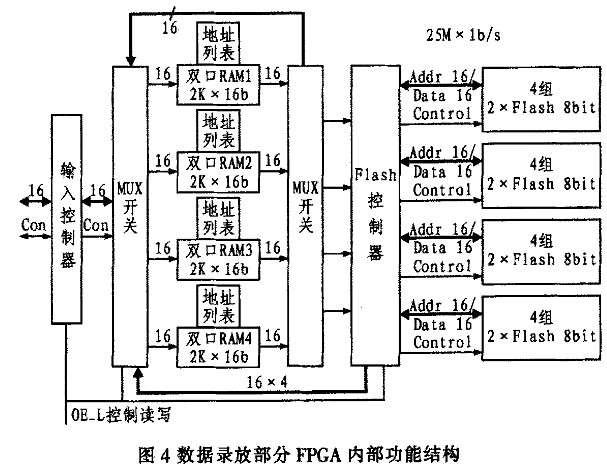

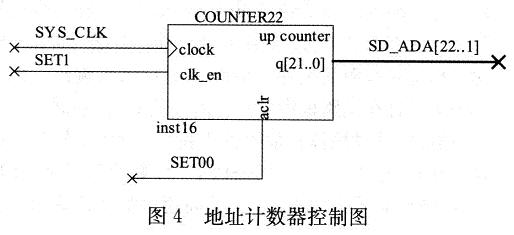

FPGA内部设计大体可划分为PCI9054操控部分和数据录放部分。PCI9054操控部分一方面跟PCI9054接口,一方面要完成对Flash的操作。数据录放部分主要完成外部数据写入、读出以及擦除、建立无产块信息列表等功能。由于对4组Flash的操作都是一样的,所以数据录放部分可以分为数据流控制部分和Flash操控部分。数据流控制部分控制数据写入或读取哪组Flash;Flash操控部分用于对Flash的具体操作。图4为数据录放部分FPGA功能结构。为了节省内部存储单元的数量,写入和读取数据要使用同样的缓存区。

3.3 无效块的建立和操作

当一个块中有一位或更多位不能正确操作时,就定义此块为无效块。无效块并不影响其他块的正常工作,各个块之间是相互独立的。所选的K9F2G08U0M在出厂时可能存在无效块,在使用中也可能产生新的无效块,但是器件的第一个块一定不是无效块。NAND Flash在出厂时就标记本身的无效块,每个块的第一页或第二页的空闲区的第一个数据不是FFh,则表示此块为无效块。为了保证Flash的正确操作,必须在操作之前建立无效块信息表。在每片FPGA中设计了4个2 048×1 bit的RAM用于存储无效块的信息。RAM的每一个存储单元存储相应总线上的4组Flash的无效块信息。其中某一块的无效块信息是4组Flash的无效块信息相“与”后的结果(1表示正常,0表示无效块)。在对Flash进行读、写或擦除操作之前,应先从RAM中读取无效块信息,然后根据无效块信息决定是否对当前块操作。

3.4 读写Flash操作

对Flash的读写操作都是基于页的,读写操作的时序分别如图5和图6所示。计算机通过CPCI总线发送出读或写命令后,FPGA内部根据接收到的命令执行相应操作。写Flash时,外部采集的数据输入RAM1,RAM1满后,开始向RAM2写入数据,同时选通第一条总线上第一组Flash的写模块,在写模块中通过计数器产生ALE、CLE、WE、RE等控制写Flash的相应时序,将数据从RAM中编程到Flash内存,并令页地址加1,依次循环(循环流程见图3)。当总线上的第4组Flash的页地址为64时,块地址加1,并读取无效块信息,如果为无效块,则屏蔽此块,重新读取下一块信息,直至读取到正常块为止。如果是正常块,则向此块中写入数据,同时将页地址清零。读操作与写操作类似,只不过是将Flash中的数据读出先送到RAM,然后依循环次序读取RAM即可。

3.5 PCI9054操控部分的设计

通过编写PCI9054专用的驱动和应用软件,实现由计算机通过CPCI总线操控存储板卡。在应用软件中,对Flash读写或者擦除等命令自定义为对CPCI总线发送特定的数据。而在FPGA内部根据PCI9054发送的局部端数据线上的特定数据判断是何种操作,并执行相应操作。FPGA和PCI9054通信的主要信号线有LHOLD、LHOLDA、READY、ADS、ADDR、DATA,利用这些信号线可以实现PCI9054局部端和FPGA握手。将数据写到计算机中。在PCI9054专用的驱动和应用软件中,利用DMA方式读取Flash,读取速度可提高至1.3 MHz×16 bit。

4 结束语

本设计采用流水、并行处理技术,利用FPGA内部嵌入的存储块设计一组高速数据缓冲区,使得多个慢速的存储器件并行工作,令系统内外部数据的速率匹配,避免了外置高速缓存,简化了硬件电路,且极大地提高了存储数据的速率。大容量高密度闪存器件可使单片存储板容量高达128 Gbit。在FP-GA内部设计中,建立Flash无效块信息列表,并在此基础上对Flash进行读、写、擦除及重建无效块信息等操作。使系统具有集成度高、灵活性好、可移植性强、速度快等特点。通过CPCI总线采取DMA方式读取,极大地提高了读取速度。当接收到的数据带宽很大,速度很高时,可将存储板并联起来,多个存储板级联可满足更大的存储容量需求,也可将级联并联二者结合起来以满足不同系统的要求。整个系统基于CPCI工控机箱,更适合于野外的工作环境,并能及时保存、分析数据。

-

FPGA

+关注

关注

1664文章

22545浏览量

640414 -

控制器

+关注

关注

114文章

17907浏览量

195707 -

数据采集

+关注

关注

42文章

8394浏览量

121346

发布评论请先 登录

常见的几种不同的高速数据采集存储系统介绍

基于FPGA的高速数据采集系统该怎么设计?

如何使用FPGA设计高速实时数据采集存储系统的资料概述

采用FPGA器件实现数据采集系统中高速大容量存储板的设计

采用FPGA器件实现数据采集系统中高速大容量存储板的设计

评论