视频和多媒体系统正变得日益复杂,因此能否获得适用于您的系统的低成本的可靠 IP 核对您的产品上市极为关键。特别是,视频压缩算法与标准已变成极为复杂的电路,需要花费很长时间来设计,并且常常成为系统测试和发货的瓶颈。这些 MPEG-4 简易 (simple profile) 编码器/解码器核也许正好能满足您下一个多媒体系统设计的需要。

应用

MPEG-4 第 2 部分是下列国际视频编码标准系列中最新的标准:H.261、MPEG-1、MPEG-2 和 H.263。该标准于 1999 年被 ISO/IEC 批准作为《国际标准 14 496-2》(MPEG-4 第 2 部分)。MPEG-4 第 2 部分视频编解码器为大量多媒体应用提供了一个卓越的基础。该标准提供了一组特征和等级,可满足大量不同应用要求,如帧尺寸和使用差错恢复工具。这些应用的例子包括广播、视频编辑、电话会议、安全/监视、以及消费电子应用。

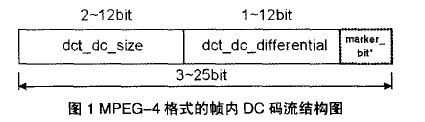

MPEG-4 第 2 部分使用的视频编码算法是从之前的编码标准发展而来。帧数据分成 16×16 个宏块,每个宏块包含 6 个 8×8 块,用于 YCbCr 4:2:0 格式化数据。采用半像素分辨率对运动进行估计可被用来对来自前一帧的预测块进行高效编码,而离散余弦变换 (DCT) 则提供了残余处理功能,以创建当前帧的更详细的视图。简易压缩标准提供 12 位分辨率的 DCT 系数,和每个采样 8 位的采样和重建帧数据。MPEG-4 简易编码的效率在一系列编码位速率下均优于在 MPEG-2 中使用的上一代的编码效率。

典型的多媒体系统可以使用 MPEG-4 在一个更大的系统中作为视频压缩组件。这种系统的一个例子就是端到端视频会议系统,它可以在两个或多个与会者之间传送压缩的位流。这些源的名称可以改变系统要求,因为会议的主要演讲者或出席者可能需要较高分辨率的视频和音频。这种类型的系统可以扩展至视频监视和安全应用,显示台用户可以决定对所有视频相机使用镶嵌幕显示,还是聚集于某个相机视图,以进行详细的实时分析。这些应用要求流的选择在接收器处进行,且能够处理实时查看规范。

MPEG-4 解码器核可以使用专门针对您的应用和系统要求而定制的可伸缩的多流接口来构建,同时 MPEG-4 编码器和解码器还可支持用户规定的最大帧尺寸。

体系结构

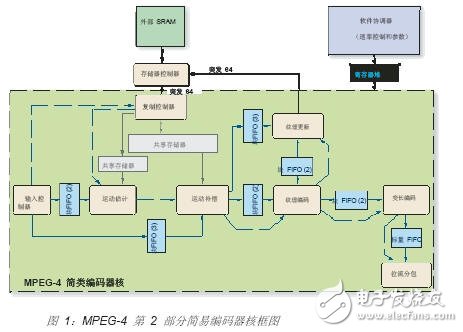

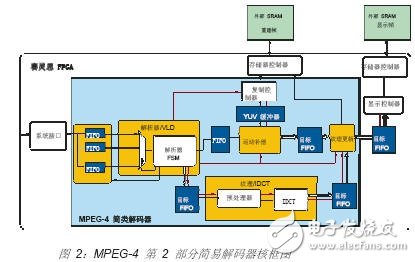

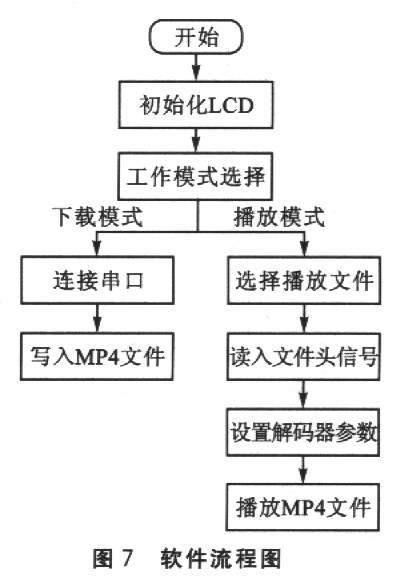

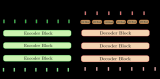

图 1 和 2 分别显示了 MPEG-4 简易编码器和解码器核的框图。这些设计采用了基于硬件的流水线架构,编码器上提供了一个主机接口,用于实现软件控制的速率控制。使用内含的存储器控制器,编码器的原始捕捉序列和解码器的重建帧被存储在片外存储器中,以便快速、低延迟地存取像素数据。它还提供了一个简单的 FIFO 接口,用于传输压缩位流,解码器可根据用户指定数量的位流定制构建。它还包含一个系统接口,以实现最大的可控制性和可观测性。

要创建可满足不同应用需求的可伸缩多流设计,随核附带的产品包中包含了大量用户指定编译时参数,从而使您可定制编码器和解码器。要创建资源高效的设计,您还可以设定最大支持帧的宽度和高度。那么编译后的设计将包含足够的存储器和寄存器,以支持低于或等于这两个参数的任意帧尺寸。其它参数可以让您对最终设计的伸缩性进行完全控制,精心构建一个专用于您的应用的系统。

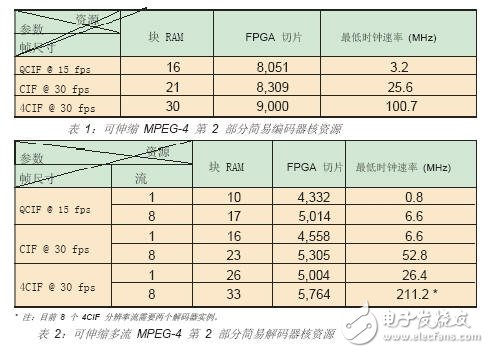

表 1 和表 2 根据对最大支持帧尺寸和解码器输入位流数量的不同参数设置列出了编码器和解码器核的 FPGA 资源。表 1 中的所有编码器设计都使用了 16 个嵌入式 XtremeDSP? 切片,而表 2 中的解码器则使用了 32 个嵌入式 XtremeDSP 切片。这些设计针对 Virtex?-4 元件,这些元件包含大量 18 Kb 块 SelectRAM? 存储器和嵌入式 XtremeDSP 切片。其它兼容 FPGA 系列包括 Virtex-II、Virtex-II Pro 和 Spartan?-3 器件。

请注意,解码器设计可以自动根据要支持的位流数实例化输入 FIFO 数和支持多路复用/分用电路。MPEG-4 编码器可实现每秒约 48,000 个宏块的吞吐率,提供了超过简易等级 5 吞吐率规范的足够动力。同时,MPEG-4 解码器设计可以保持每秒约 168,000 个宏块的吞吐率,提供了对两个逐行 SDTV(720×480,60 fps)视频流或 14 个 CIF 分辨率视频流进行解码的足够吞吐率。该解码器吞吐率是等级 5 简易编码器和解码器核所需吞吐率的四倍以上。

结论

MPEG-4 简易编码器与解码器核采用独有的、可伸缩的、多流功能设计,以满足您的特定系统需求。大量的不同应用可以在多媒体系统中利用这些核,包括视频会议、安全与监视、以及您要向世界展示的任何令人激动的新消费应用。

这些视频设计采用了高吞吐率、流水线架构以及足够的可定制参数,以创建专用于您的应用的资源高效的设计。

-

FPGA

+关注

关注

1631文章

21811浏览量

606877 -

解码器

+关注

关注

9文章

1154浏览量

41000 -

编码器

+关注

关注

45文章

3682浏览量

135444

发布评论请先 登录

相关推荐

基于可编程逻辑器件实现MPEG-4简易编码器和解码器核的设计

请问哪位大神可以分享一个支持ipcores的xilinx fpga:mpeg-4编码器?

TMS320C6201 在MPEG-4 视频解码器中的应用

MPEG-4 ASP视频编码器的软件优化设计

基于FPGA NiosII的MPEG-4视频播放器

MPEG-4实时编码器在ADSP-BF533上的实现

基于MPEG-4的视频DCT编码器的实现

基于FPGA仿真结果的MPEG4可变长数据解码器设计详细概述

下载适用于Blackfin软件的MPEG-4 HEA-AAC v2解码器评估版本

基于transformer的编码器-解码器模型的工作原理

基于 Transformers 的编码器-解码器模型

基于FPGA实现MPEG-4简易编码器与解码器的设计

基于FPGA实现MPEG-4简易编码器与解码器的设计

评论