随着数字电视技术的进一步成熟,在视频服务器方面,利用支持软件丰富、运算速度不断提高、具有较高性能价格比的微机来代替昂贵的专用设备实现数字视频码流的复用具有一定的实际意义,但是一般的桌面操作系统定时不够精确、处理大量并发任务效率不高以及突发传送等问题影响了复用后码流的质量,为了保证复用后的码流可以均匀平滑地传送到调制器,还考虑到微机的工作效率,就需要用FIFO来进行码流的缓冲。如果FIFO的容量足够大,微机就可以通过DMA方式一次发送大量的数据,最后再经过FIFO的缓冲,按照预设频率均匀送出。

在其它许多实际应用中,也会利用到FIFO来完成数据流的缓冲,消除突发传送带来的数据抖动,达到平滑输出的效果。FIFO的容量和速度直接影响到缓冲的效果,但是目前大容量FIFO价格昂贵,这就影响到了FIFO的进一步实际应用。本文介绍了一种利用外部SRAM和CPLD构成的廉价、高速、大容量先进先出缓冲器FIFO的设计方法。

一、系统的设计思路

为了用外部SRAM来实现FIFO,要解决以下问题:

区分同时到达的读写信号,并且产生间隔的对外部SRAM的读写信号

在SRAM顺序寻址的基础上实现数据的先进先出

全空、全满、半空、半满状态的判定

尽量降低对器件速度的要求

二、设计方法

同步设计

在系统中地址产生、比较器结果输出、FIFO各种状态的输出都采用同步触发方式,全部按照系统时钟统一进行,这能在很大程度上消除异步方式引起的逻辑状态变化时间的不确定和毛刺的产生,但也没必要在所有的地方都强求按同步设计,只要能符合时序要求,异步方式也可以,目的是尽量减少设计的复杂度和占用的资源。

原理图输入

设计在Altera公司的MAX+plus II V9.6软件下编译仿真。在系统的整体设计中采用原理图的方式,可以方便地进行时序控制和仿真。

三、具体信号的产生及时序分析

信号分析的具体条件

以下的设计都是在CPLD为EPM7128SQC100-6,SRAM为IDT71128-12的条件下进行,对FIFO的最高要求为双向同时读写,时钟RCLK和WCLK为10MHz,脉冲宽度为50ns,系统时钟CLK为50MHz,脉冲宽度为10ns。对于较低速度的读写,50MHz的系统时钟也可以适应,如果外部要求降低,也可按照与RCLK、WCLK的等比例换用较低的系统时钟。外部数据是在上升沿有效,FIFO的输出也是上升沿有效。

基本信号的产生以及时序图

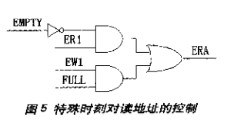

系统采用独立的系统时钟CLK。为区分同时到达的外部读写信号,内部产生的读写信号分别用系统时钟的上升沿和下降沿触发,同时让产生的内部读写信号互斥,以得到间隔的对外部SRAM的读写信号;考虑到实际的需要以及器件和内部时钟的速度,按照四个脉冲宽度的方式产生读写信号,以保证在最小10个脉冲时间内各有一次有效读写。

外部读写时钟RCLK、WCLK先经过各自的使能控制信号REN、WEN进入CPLD;为保证读写互斥,外部读写异步锁存之后,读信号锁存后面的第一个上升沿,写信号锁存后面的第一个下降沿,并且用各自的前三个脉冲控制对方锁存第一个脉冲。

通过对各种情况的分析,基本读写脉冲OE和MW之间的最小间隔是一个脉冲,在有连续两个外部读或写的情况下所产生的两个OE或MW之间的最小间隔是两个脉冲。

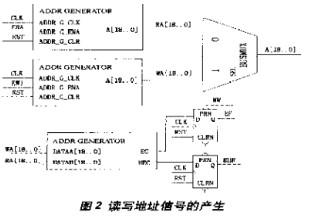

读写地址信号

读写各有一个地址指针,每读出一个数读地址加一,读指针就指向下一个最早写入的数,经过SRAM阵列的最高地址后,又从起始地址开始,这样就可以达到先进先出的效果;只有有效的读写脉冲才能触发地址计数器;为使整个系统的动作时间一致,采用同步设计,读写都统一选择上升沿触发计数器变化;地址改变先于后面的/WE、/OE脉冲的产生。

地址发生器采用计数器宏单元。FIFO容量的大小由计数器决定,简单地增加计数器的位数和SRAM的数量,就可以扩大FIFO的容量。读写地址产生之后,经过一个总线复用器后输出作为对外部SRAM读写的地址线;总线复用器的选择由MW信号控制,只有在MW有效的时候才输出为写地址,其它时间都是读地址。

读写地址在由计数器产生经过总线复用时,会产生静态冒险;对于读写地址比较器,因为它锁存的时刻距离地址变化后两个脉冲,而且比较器输入的地址不经过总线复用,这就可以保证在比较器锁存的时刻地址比较结果已经稳定而且不受静态冒险的影响;对于到SRAM的读写地址,在读写控制脉冲/OE、/WE有效前还有两个脉冲的时间稳定,不会因为地址不稳定产生错误操作。

读写地址相等时比较器输出相等标志EF,FIFO半满,即除去最高位以外的地址都相等的情况输出半满标志EHF。

FIFO状态信号

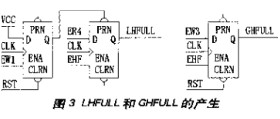

1、小于半满LHFULL

在上电或复位之后,LHFULL立刻有效。利用另一个触发器上电或者复位的清零,置位LHFULL触发器,使其有效,但在第一个写之后这个触发器就不再对LHFULL的变化有影响。在读写地址比较器输出半满的时候再来一个读,就判定为小于半满LHFULL。从大于半满到小于半满,需要经过两个连续的读,第一个读使比较器得到半满结果,第二个读使LHFULL有效。当经过一个写从小于半满到半满时,在读写地址比较器输出半满使LHFULL触发器状态可以变化后的下一个上升沿清除LHFULL触发器。触发器的使能端选为EHF,保证状态信号只在半满的时候才发生变化。

2、大于半满GHFULL

半满的时候再来一个写,GHFULL置位为高有效。GHFULL的设计原理同LHFULL,且不需要上电复位置位的处理。

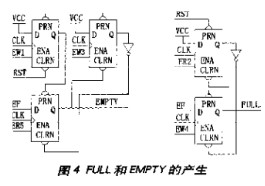

3、全满FULL

当比较器输出结果为读写地址相等时,如果此时执行的操作是写,即在一个写之后读写地址才相等,就判定为全满,置FULL为有效。在全满状态下,如果有一个读,FULL就被清零。

1、 全空EMPTY

在上电或复位之后,EMPTY立刻有效。利用另一个触发器上电或者复位的清零,置位EMPTY触发器,使其有效,但在第一个写之后这个触发器就不再对EMPTY的变化有影响。当比较器输出结果为读写地址相等时,如果此时执行的操作是读,即在一个读之后读写地址相等,就判定为全空,置EMPTY有效。全空状态下,如果有一个写,EMPTY就被清零。

复位信号

只要RST信号为低就会产生有效的复位,读写的地址计数器都被清零,全满、大于半满状态清除,全空和小于半满置位,FIFO锁存输出为零。

与外部SRAM的连接及对SRAM的读写定时分析

CPLD与SRAM之间除去读写复用的地址和数据线以外,还需要有输出使能信号/OE,读写信号/WE,片选信号/CS。地址线、数据线、/OE和/WE如前所述;片选信号由地址高位译码产生,在这里是把最高位取反,得到两个片选信号。

读写信号的时序符合设计采用的IDT71128-12 SRAM的定时要求。

写操作:

写周期最小12ns,地址有效到结束写最小10ns,片选到写结束最小10ns,写脉冲最小10ns,数据有效到写结束最小7ns。地址在/WE之前建立,在/WE结束之后变化;数据保持到/WE无效再变化;在地址变化时,/WE、/CS不能都有效;在有效的写时,/CS、/WE为低;

读操作:

地址寻址时间最大12ns,读周期最小12ns,片选寻址时间最大12ns,输出使能到数据输出有效最大6ns。在读周期/WE为高,/OE为低,读周期结束时地址和数据应该保持不变。

写地址与MW脉冲的上升沿同时变化,在两个脉冲之后,写地址能够稳定,这时/WE才有效,并且由于连续两个读写脉冲之间最少有一个脉冲的间隔,而且MW比EW4要有延迟,同时总线选择也是由MW决定,就保证了写地址在/WE前有效并能保持到/WE结束;写数据的三态缓冲由EW4打开,可以保持到/WE结束。

读地址在上一个写结束之后有效,由于读地址变化比OE脉冲晚一个脉冲,/OE在OE结束时开始,保证了/OE开始的时候读地址已稳定和读周期时间符合要求;写数据已由EW4关闭,由于读写之间的。

-

cpld

+关注

关注

32文章

1248浏览量

169431 -

缓冲器

+关注

关注

6文章

1923浏览量

45527 -

操作系统

+关注

关注

37文章

6847浏览量

123424

发布评论请先 登录

相关推荐

利用外部SRAM和CPLD构成先进先出缓冲器FIFO的设计

利用外部SRAM和CPLD构成先进先出缓冲器FIFO的设计

评论