作者: 廖涌,程曦

在被测点阻抗较高时,即使该点仅有较小的电容,其带宽也会受限。在基于磁簧继电器的多路选择器中,由于各磁簧继电器的寄生电容会在输出端并联,加大了输出端的电容,使得电路的带宽变窄。本文介绍了可消除这种寄生电容的电路设计方案。

多路选择器是一种能从多路输入信号中选出一路并将其输送至输出端的一种器件。在测试自动化领域,它可以取代人工插拔线路,且能使一台单输入仪器自动测量多个信号,从而降低测试成本,节约测试时间。实现选择器的一种常用方法是使用磁簧继电器。磁簧继电器具有体积小、较半导体继电器导通电阻小且较电磁继电器反应速度快等优点。这些特点使得磁簧继电器受到各种选择器模块的青睐。

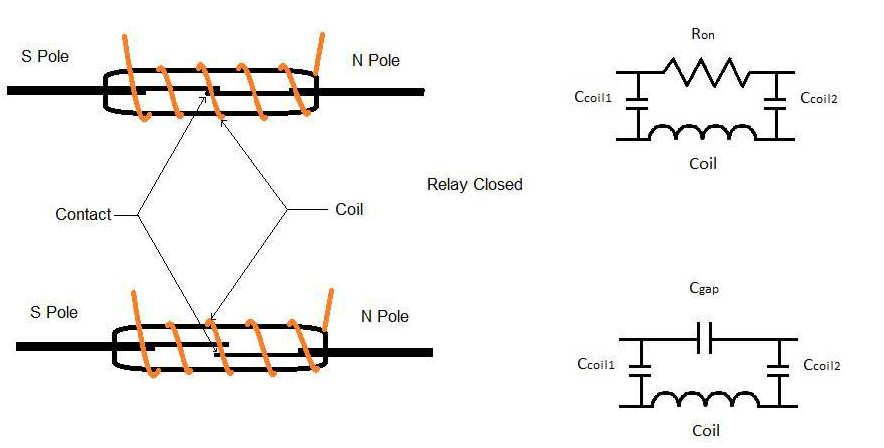

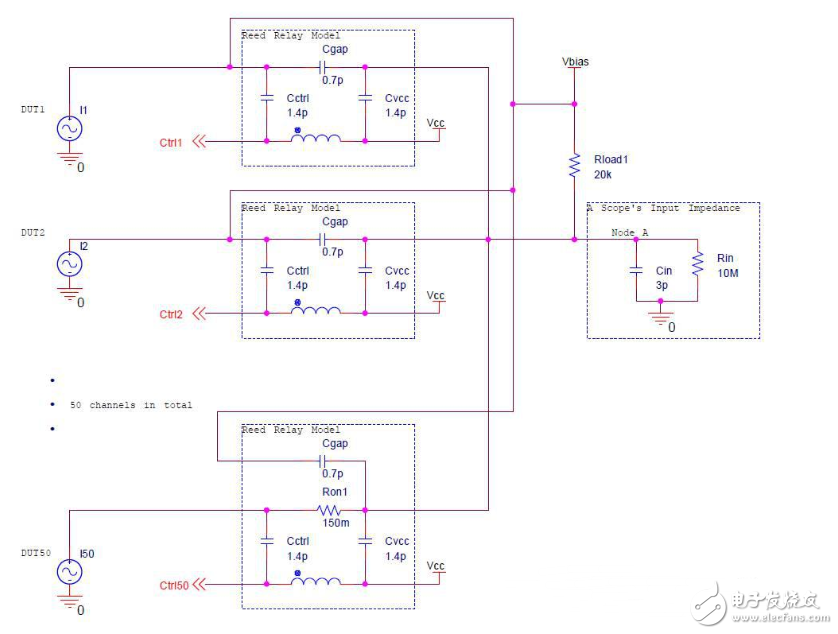

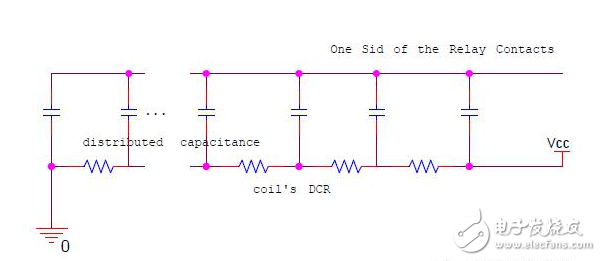

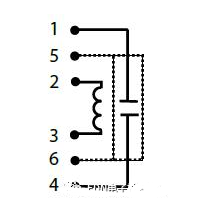

磁簧继电器的结构及等效电路如图1所示。其非理想性主要源于其导通电阻(Ron)、两根干簧管间的开路电容(Cgap)以及干簧管到线圈间的电容(Coil1,2) 。不过这些非理想性在大多数情况下都是可以忽略的。下面我们用一个例子来说明这一点。

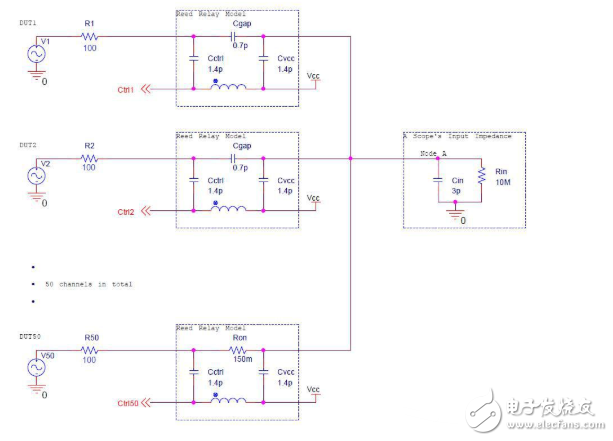

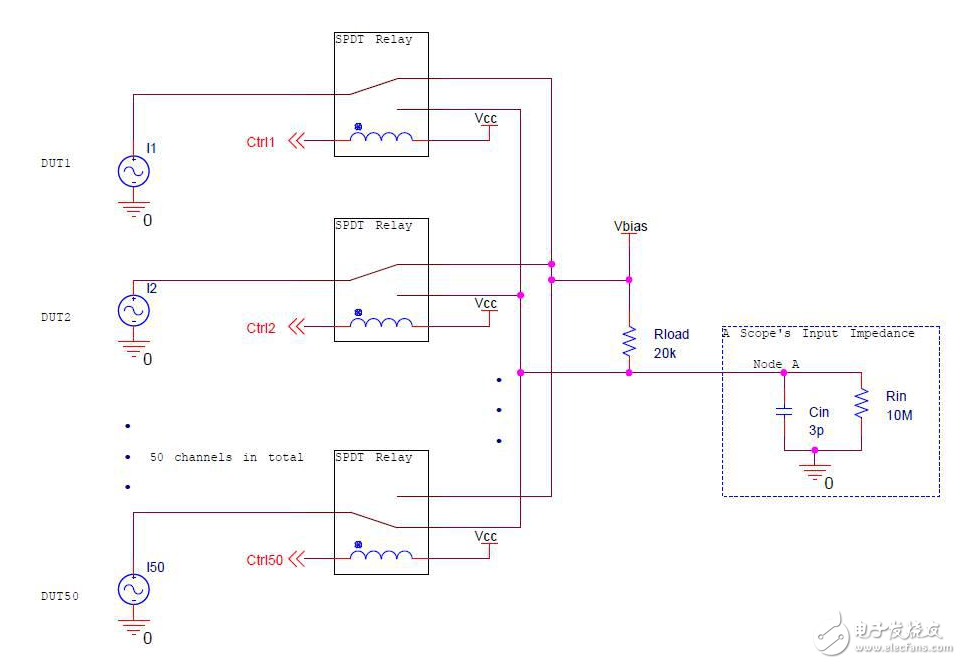

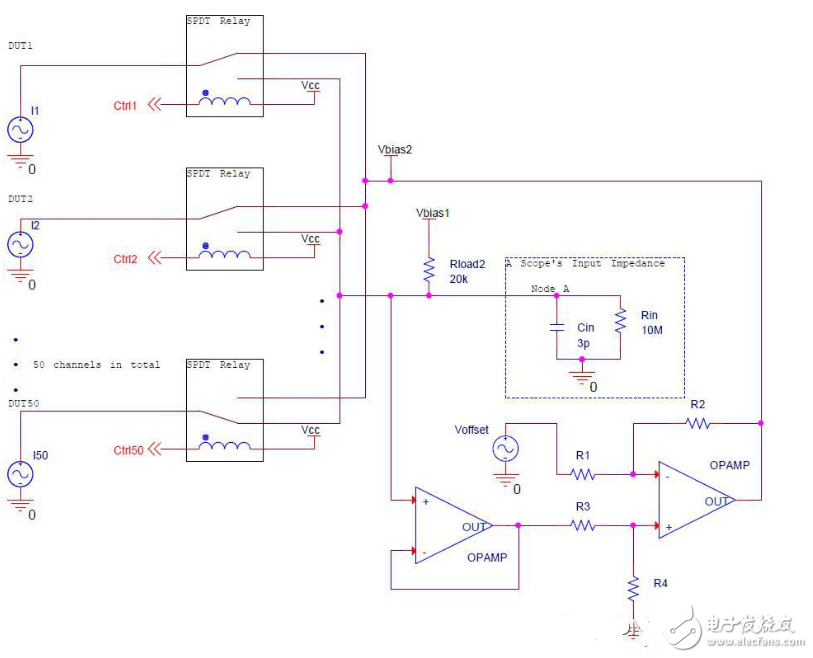

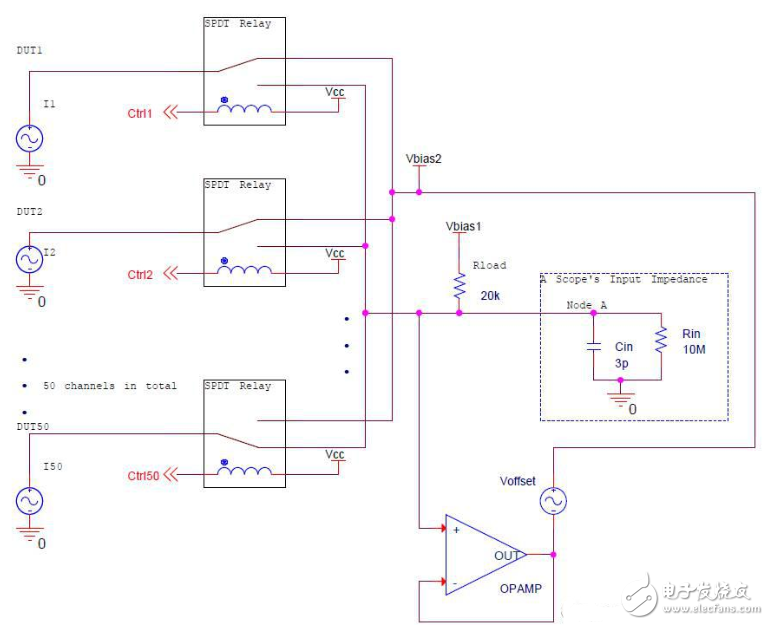

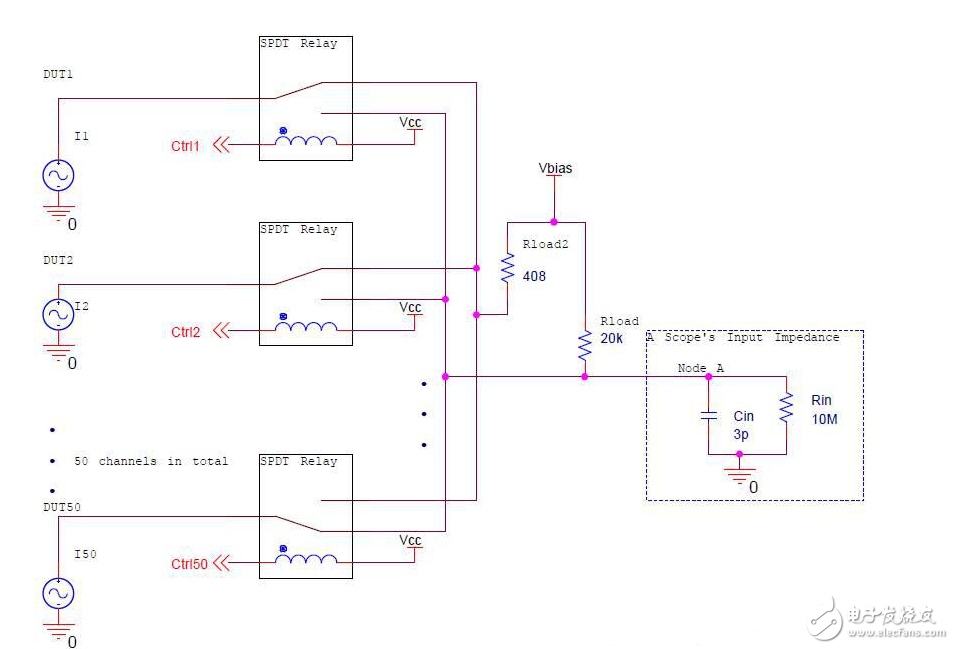

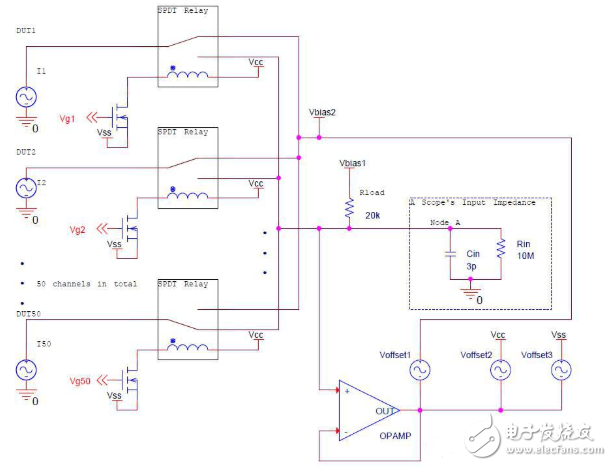

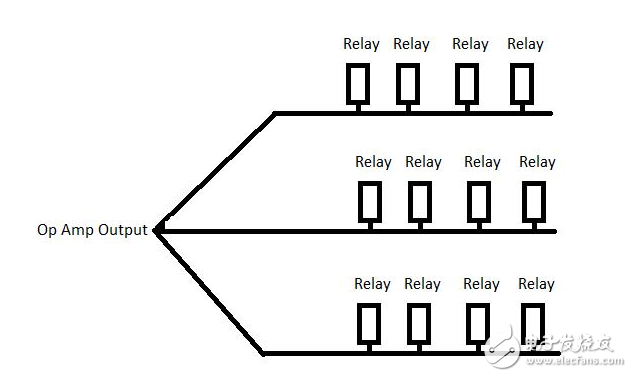

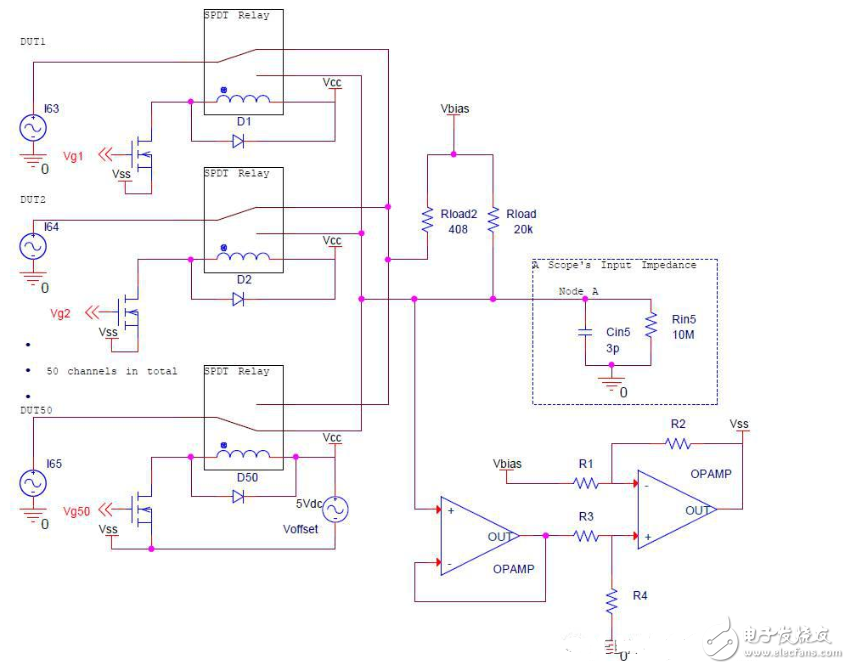

图2所示为基于继电器的多对一选择器的典型应用电路。 Vcc为线圈偏置电压,Ctrl n ( n = 1, 2, … , 50) 连于驱动电路(图中略去)。Cvcc和Cctrl 是位于继电器管脚之间和管脚与线圈之间的等效电容。与100Ω串联的电压源代表被测器件的输出端,3pf 电容并联10MΩ电阻则为等效示波器的典型输入阻抗。图中的电路有50路输入端,第50路输入端通过继电器连接于示波器,其它49路则处于开路状态。

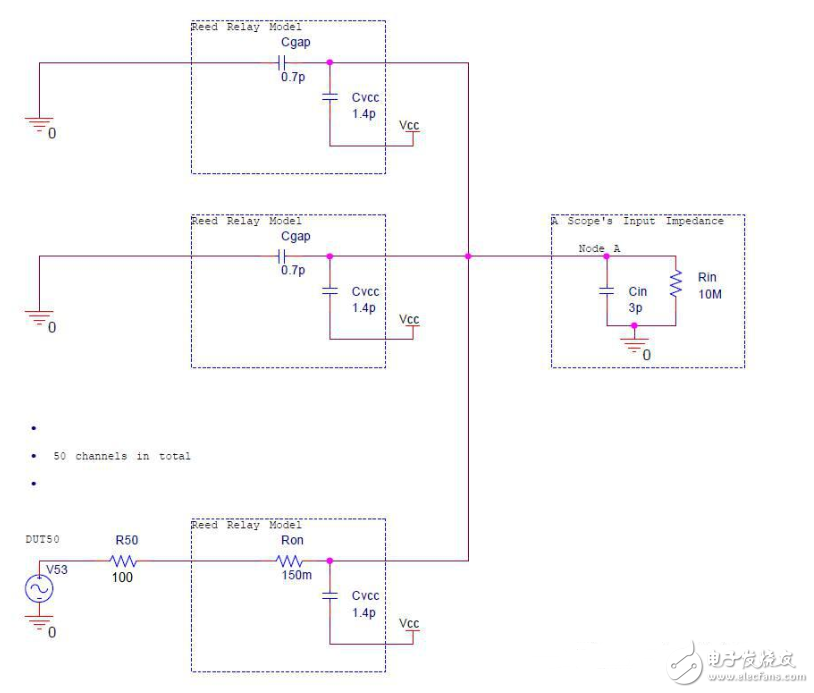

对于以上电路,输入电压的频率需要多大,才会使得示波器量得的信号明显有别于实际电压输入信号呢?为了计算这个问题,我们首先来简化一下上面的电路网络。我们注意到,点A的对地电容是该网络各节点中最大的:其上有50个1.4pf Cvcc并联接地。所以,在该网络的-3dB频率,点A的对地阻抗应该接近于100Ω的电压源输出电阻。由于继电器开路电容Cgap远远小于点A对地电容,相同频率下,可近似于开路。这样,与之串联的100Ω电阻也都可以忽略了。同理,Cctrl50也可视为开路。这样,我们就得到了如下简化电路 :

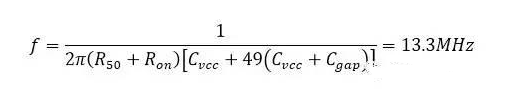

该简化网络的-3dB频率为:

可见,对于数兆赫以下的中低频应用场合,基于磁簧继电器的多路选择器可近似为理想导线。

高阻测试点应用

然而,当被测仪器的输出阻抗较大时,情况就不同了。我们还是来举一个例子。如图4所示 (等效电路见图5),该网络与图3几乎一样,唯一的区别是被测器件的输出由电压源变成了电流源。为了不让任何一个电流源开路,这里使用了单刀双掷型继电器。Rload将电流转为电压,以供示波器测量。假使继电器寄生元件参数不变,由于Rload有20KΩ的电阻,该网络-3dB频率将降到仅60kHz左右。在实际应用中,由于PCB和线路的电容,其-3dB频率会更低。这样一来,即使对低频电路,这样的多路选择器也变得不再适合了。

尽管上述分析使用了电流源,但在被测器件是输出电阻较大的电压源时也会发生以上情况。

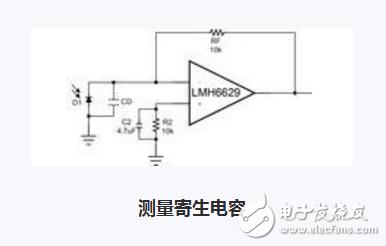

下面,我们将介绍一种可基本消除点A电容的电路。使用该电路后,上述多路选择器的频率可被拓宽数十倍,因而可应用于高阻抗测试点。减少电容不单可以增加带宽,在被测端接反馈网络的情况下 (比如运放输出端),也可以改善稳定性。此外,小电容也有利于测试输出端的阶跃响应。总之,在选择器的输出端减小电容,有明显的好处。

电容消除电路

我们接下来会介绍若干种方法来减小A点的电容。我们使用电流源电路来说明这些方法,但是这些方法也可用于电压源电路。

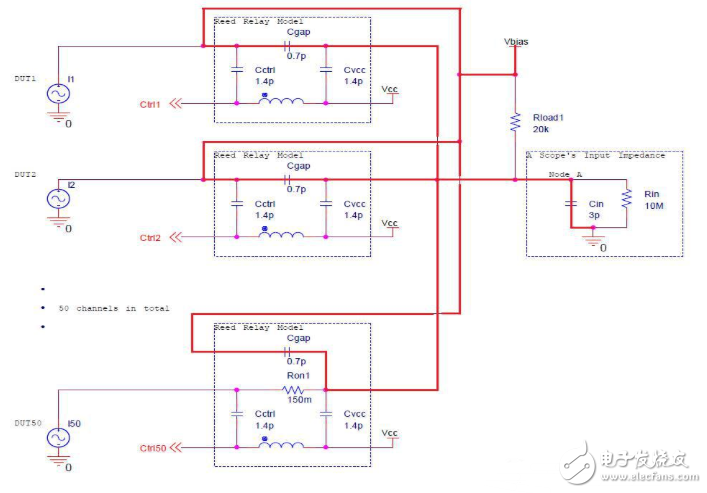

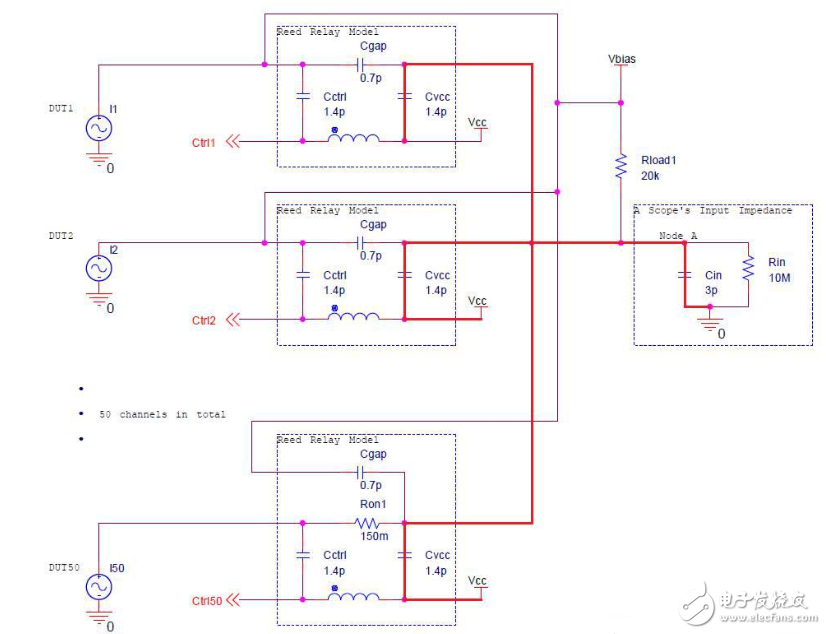

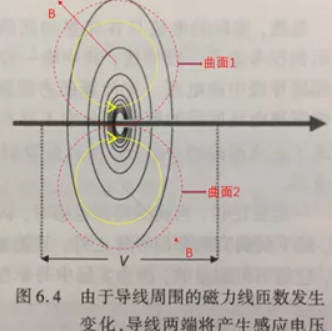

为了思考这一问题,我们首先需要找出这些寄生电容的成因。经过观察,我们不难发现点A的寄生电容主要有两个来源。图6和图7绘出了容性电流的通路。显然,解决问题的关键就在于阻断这两条容性电流通路。我们接下来就分别研究这两条通路。

消除Cgap

首先我们来看图6。这一通路流经50个并联的继电器开路电容Cgap,回到交流地Vbias。50个Cgap并联,形成了一个较大的电容。

也许你会问,为什么不关闭不用的电流源,这样不就不需用单刀双掷继电器,而用单刀单掷的就可以了?这样,Cgap的问题不就不存在了吗?遗憾的是,事实并非如此。

首先,即便电流源关闭,它还是会有并联寄生电容。该电容可以在高频将其接地。

其次,即便电流源的输出电容很小,Cgap还是会连到Cctrl,而Cctrl则会连到驱动电路,驱动电路上还有线圈续流复位二极管。这些电路的电容会通过Cctrl接地,而这些电容一般与Cctrl相当,或更大。所以点A由于Cgap并联而有的电容值还是会很大。

因此,我们将保留单刀双掷的设计。之后我们将看到,这样的设计将便于实现电容消除电路。 回到消除Cgap的讨论。电容的电流是由电容两端电压变化引起的。

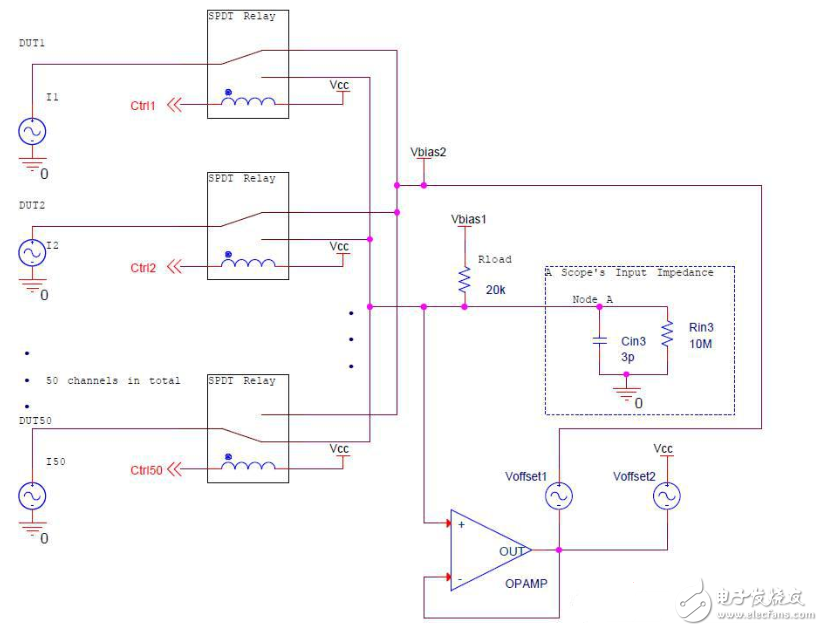

既然点A的电压必须变化,那我们能不能使得电容的另一端不接地(交流地),而接到与A一齐变化的电位上呢?顺着这样的思路,我们得到了如图8的电路。

图8中,点A的信号经过运放隔离后,加上一个直流偏置,被回送到Vbias2。右边的运放输出为:

Voffset 是直流电压偏置,其值可正可负,作用是给不使用的电流源一个合适的直流电压偏置值。

图8的方法需要两个运放(除非Voffset为0)。如果Voffset为0,另一运放可直接连到Vbias2。实际上可以省去一个运放,图9给出了使用一个运放和一个浮动电源的电路。

好在许多常见的实验室电源都是浮动的:其输出端由变压器隔离。比如Keysight E3631A和E3646A,其负极和地之间的电容在我们所讨论的应用中可以忽略。

图9虽然省了一个运放,但还是需要有源元件。图10给出了只需一个电阻就可以达到类似效果的方案,该方案仅在特殊情况下成立,但此特殊情况却并不罕见:

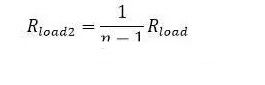

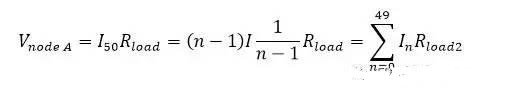

如果选择器上的每一个被测器件都相同,并且可以在不被测时同时开启,那么我们就能使每个被测器件输出同样的波形。Rload2的值为:

式中,n是被测器件的总数,在我们的例子里是50。

I是单个被测器件的输出电流,In = I (n = 1,2,…50)。

可见,这将使得Cgap两端的电压保持不变,从而切断容性电流的通路,Cgap也就不再影响点A了。

消除Cvcc

研究完消除Cgap的电路,我们再来研究如何消除Cvcc。这一通路主要由许多Cvcc构成,最终流回了Vcc——继电器线圈的直流偏置电压。有了之前消除Cgap的经验,我们不难得到一个类似的电路。图11用一个浮动电源来达到消除Cvcc的效果。

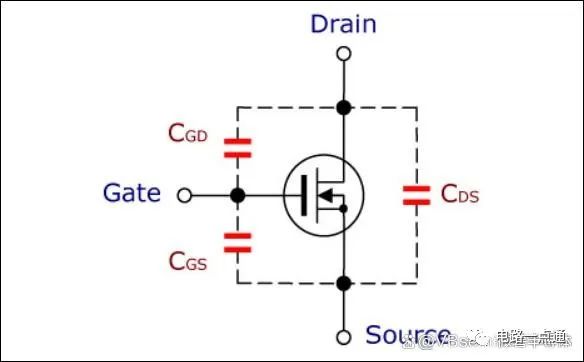

这样一来,似乎我们所有的问题都应该解决了。很遗憾,实验结果表明,上图的电路并不能消除所有的Cvcc。何以如此呢?我们需要再仔细观察一下继电器线圈的模型。

继电器线圈虽然被画成了电感,但实际上却有较大的直流电阻,大约在100Ω量级。我们已经指出,继电器驱动电路有较大的电容。简单起见,我们考虑一种极限情况:驱动电路的电容很大,以至可以认为线圈的一端直接接在交流地上,那么继电器管脚和线圈之间的电容就会沿着干簧管分布,如图12所示。也就是说,只是在Vcc上加上信号并不能抵消所有的管脚和线圈之间的电容。

图13的电路解决了这一问题(为了简单起见,图中略去了续流二极管)。Vss为点A交流部分的信号加上0直流偏置,这样继电器线圈的两端就都被和点A相同的交流信号驱动,Cvcc对点A就不再影响。

你也许已经注意到了,图13中驱动电路的源极不再是地。这样一来,栅极驱动电压还能可靠地打开驱动电路吗?的确,图13中的电路只能在栅极电压减去源极电压最大值后依然大于驱动电路开启电压的情况下工作。否则,我们就需要增大栅极电压,直到足够为止。

其他注意事项

至此,我们用理想电路模型讨论了消除磁簧继电器寄生电容的电路技巧。然而,实际的电路并不是理想情况。所以,为了使以上电路达到较好的效果,还有许多工程实践的细节需要考虑。

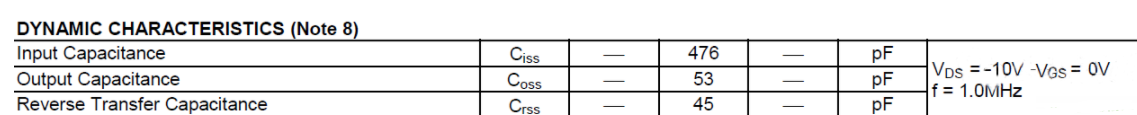

继电器选取

虽然电路可以消除寄生电容,但是我们还是应该选取寄生电容较小的继电器,因为继电器的电容会成为运放的负载。对于非理想运放,电容负载小,相应的相移和幅值损耗也小。这样,电路消除电容的效果也会更佳。

另外,在图10 中,等效来说,每路电流源仍需驱动一个继电器的Cgap,所以小的寄生电容总是好的。

继电器的屏蔽层

继电器屏蔽层是线圈和管脚之间的一层金属,主要用于屏蔽噪音 (这里指的不是磁屏蔽层) 。大多数情况下,屏蔽层会接地或交流地。该层会减小管脚之间和管脚到线圈的电容,但是会增加额外的管脚到屏蔽层之间的电容。如果继电器有屏蔽层,可以用对线圈Vcc一样的方法处理。

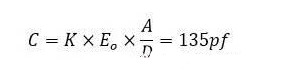

电路板布线

标准PCB FR4 材料有4.1-4.4的介电常数。如果相邻两层有30mm X 30mm、相距10mil(0.254mm)的铜皮,那么它们之间的电容为:

Eo = 8.854x10-12,K = 4.3,A为面积,D为距离。

对于有50个磁簧继电器的PCB,连接继电器各管脚的铜线不可避免会占一定面积。所以在这些线下,不要铺铜,以减少电容。

由此产生的一个副作用是电路的抗噪音能力变差了。所以如果必要,可以在电路外部加装噪音屏蔽盒。

连接运放输出端至各继电器时,扇出(fan-out)和菊花链布线法各有千秋。扇出法意味着线路总长度更长,即铜线形成的电容更大。好处是各个继电器的铜线电容大小类似,消除电容电路对各个继电器的效果也就更接近。

反之,菊花链能使总线最短,使得运放负载电容变小,代价是各个继电器消除电容的效果参差不齐。 因此我们建议使用混合布线,如图15所示:

实验

我们使用图16的电路制作了一个多路选择器来测试博通的一款多路电流源产品,该产品电流源DC成分为0。实验中使用一台三端Keysight E3631A电源提供运放的电源和Voffset,以驱动继电器。

在文中所述的电容消除技术被使用之前,选择器实测点A电容约300pf, 改进布线后减至约200pf。Rload2加入后,电容降至约150pf。使用AC+DC驱动Vcc后,电容继续降至约30pf。在继电器驱动源极也被驱动后,点A电容仅余不到10pf。剩余的10pf很可能来自接口和连接线。-3dB频率增加30余倍。

总结

在被测点阻抗较高时,即使该点仅有较小的电容,其带宽也会受限。在基于磁簧继电器的多路选择器中,由于各磁簧继电器的寄生电容会在输出端并联,加大了输出端的电容,使得电路的带宽变窄。本文介绍了可消除这种寄生电容的电路设计方案,使用该方案,如果设计合理,选择器的输出端电容可以降为小于单个磁簧继电器的寄生电容。该方案的中心思想是使用与被测信号有同样交流成分的信号,驱动寄生电容的另一端。这可以通过运放、浮动电压源、甚至电阻来实现。除了拓宽带宽,该设计也可通过降低电容使得被测电路稳定性受到更小的影响并更好地测量阶跃响应。

-

电路

+关注

关注

173文章

5979浏览量

173129 -

电容

+关注

关注

100文章

6100浏览量

151203 -

多路选择器

+关注

关注

1文章

22浏览量

6565

发布评论请先 登录

相关推荐

MOSFET寄生电容参数如何影响开关速度

PCB寄生电容的影响 PCB寄生电容计算 PCB寄生电容怎么消除

如何消除寄生电容的影响

什么是寄生电感_PCB寄生电容和电感计算

什么是寄生电容_寄生电容的危害

可消除这种寄生电容的电路设计方案资料下载

MOSFET的寄生电容及其温度特性

PCB寄生电容的影响、计算公式和消除措施

如何消除寄生电容的电路设计方案

如何消除寄生电容的电路设计方案

评论