双锁相环邻频调制器制作,Phase-locked loop

关键字:锁相环调制器电路图

作者:林德耀

本制作是在单片机控制下,通过复位开关对双锁相环邻频调制器输出的电视频道进行递增或递减的切换,基于上期(09年第七期)所描述的双锁相环邻频调制器设计与制作的基础上,在MC145152AP、MC12022锁相分频的环节上,对电视频道的本振频率(比欲设频道的图像载频高38MHz)进行数字编码,根据编码规则所获得的信息进行C语言的程序设计。仿真测试通过后将程序烧录在AT89C52单片机芯片内,制作成的电路通过两个复位开关进行电视频道的切换,并将有关数据显示在LCD液晶显示屏上。

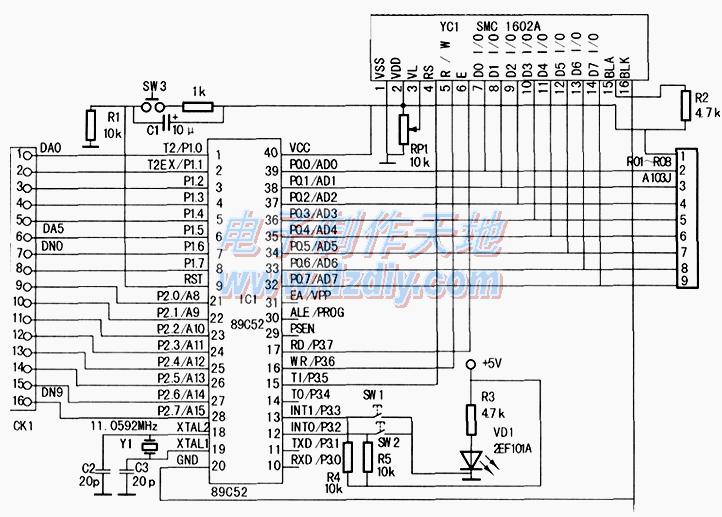

一、单片机控制电路原理

单片机控制电路如下图所示,SW3为复位开关,当按下复位开关SW3时,电路复位,单片机处于起始工作状态(1CH);按下复位开关SW1或SW2,双锁相环邻频调制器输出的电视频道分别作步进递增或递减的变换。

一、单片机控制电路原理

单片机控制电路如下图所示,SW3为复位开关,当按下复位开关SW3时,电路复位,单片机处于起始工作状态(1CH);按下复位开关SW1或SW2,双锁相环邻频调制器输出的电视频道分别作步进递增或递减的变换。

所有的这些信息传递,都是经系统软件处理后由P1、P2口输出欲设频道本振频率相应的数字编码信息至CK1插座上,CK1插座与上期(09年第七期)所描述的MCl45152AP相应端口相连,迫使双锁相环邻频调制器根据人们的意愿进行电视频道的切换,并在LCD液晶显示屏上显示当前所设置的频道数和本振频率。

数字编码信息与LCD液晶显示屏所显示预设频道数及本振频率对应关系一览表如下表所示。

|

频道数

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

发布评论请先 登录 相关推荐 锁相环是什么意思锁相环(Phase-Locked Loop,简称PLL)是一种广泛应用于电子系统中的反馈控制系统,主要用于频率合成和相位同步。本文将从锁相环的工作原理、基本组成、应用案例以及设计考虑等

可编程晶振的锁相环原理锁相环(Phase-LockedLoop,PLL)是一个能够比较输出与输)入相位差的反馈系统,利用外部输入的参考信号控制环路内部振荡信号的频率和相位,使振荡信号同步至参考信号。而锁相环

锁相环PLL在无线电中的应用 锁相环PLL与模拟电路的结合锁相环PLL在无线电中的应用 1. 频率合成 在无线电通信中,频率合成是生成所需频率信号的关键技术。锁相环可以用于生成稳定的频率输出,这对于调制和解调过程至关重要。通过调整PLL的参考频率和反馈路径

锁相环PLL技术在通信中的应用锁相环(Phase-Locked Loop,PLL)技术在通信领域中具有广泛的应用,其核心是一个反馈环路,通过不断比较输入信号和反馈信号的相位差来调整输出信号的频率,使其与输入信号同步。 一、PLL

锁相环PLL的工作原理 锁相环PLL应用领域锁相环(Phase-Locked Loop,简称PLL)是一种电子电路,它能够自动调整输出信号的相位,使其与输入信号的相位同步。这种电路在电子工程领域有着广泛的应用,特别是在频率合成、时钟恢复、

简述锁相环的基本结构锁相环(Phase-LockedLoop, PLL),是一种反馈控制电路,电子设备正常工作,通常需要外部的输入信号与内部的振荡信号同步,利用锁相环路就可以实现这个目的,它可用来从固定的低频信号生成稳定的输出高频信号。

锁相环频率合成器的特点和应用锁相环频率合成器(Phase-Locked Loop Frequency Synthesizer, PLLFS)是一种利用锁相环(Phase-Loc

锁相环和锁相放大器的区别锁相环(Phase-Locked Loop, PLL)和锁相放大器(Lock-in Amplifier)是两种在电子学和信号处理领域广泛应用的技术,它们各自具有独特的工作原理、组成结构

锁相环相位噪声的影响因素锁相环(Phase Locked Loop, PLL)相位噪声是评估锁相环性能的重要指标之一,它描述了输出信号相位的不稳定性。相位噪声的存在

锁相环的工作原理和应用场景锁相环是一种利用相位同步产生的电压,去调谐压控振荡器(Voltage Controlled Oscillator, VCO)以产生目标频率的负反馈控制系统。它基于自动控制原理,通过外部输入的参考信号

AD9694输入时钟低于337.5MHz时,serdes锁相环无法锁定怎么解决?我在配置AD9694的过程中遇到了AD9694输入时钟低于337.5MHz时,内部的serdes锁相环无法锁定的问题;但输入时钟高于337.5MHz时,如400M、600M就能锁定;0x56e寄存器

发表于 06-21 14:27

倍频器与锁相环的区别 在电子和通信领域,倍频器和锁相环(PLL)是两种常见的电路结构,它们在信号处理、频率合成和通信系统中扮演着重要角色。尽管两者在某些方面存在相似之处,但它们在功能、工作原理和应用领域等方面存在显著差异。本文将对倍频器和

锁相环的基本原理和主要作用锁相环(Phase Locked Loop,简称PLL)是一种在电子系统中广泛应用的负反馈控制系统,其主要作用是实现输入信号与输出信号之间的相位同步。在现代通信、雷达、导航、测量等领域

|

双锁相环邻频调制器制作,Phase-locked loop

双锁相环邻频调制器制作,Phase-locked loop

评论