关键字:CD4093,逻辑测试电路

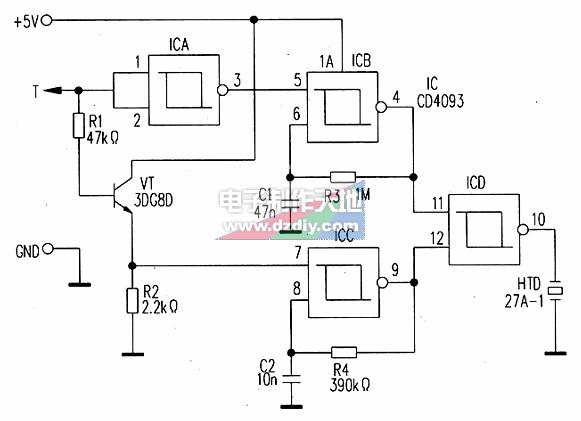

电路如图所示。由4个二输出端与非门,一只晶体管组成,并采用压电陶瓷蜂鸣器发声,根据音调不同判断被测逻辑状态。

电路原理:电路中由与非门ICB、R3、C1组成“0”振荡器,与非门Icc、H4、C2组成“1”振荡器,R3、C1或R4、C2取值不同时,振荡器的频率也不同。ICB的⑤脚和ICC的⑦脚是控制端,加高电平“1”时振荡器工作,输出矩形波。该逻辑笔的检测状态为:(1)当探针T未检测或检测到“悬空”状态时,I—CA输出“0”(一般认为逻辑门输入端开路时,输入为“1”)。同时VT截止,ICC的⑦脚被R2下拉为“0”,“0”振荡器和“1”振荡器均停振,ICD无输出,蜂鸣器HTD不发声:(2)当探针T检测到“0”时,VT截止,Icc的⑦脚为“0”,“1'’振荡器不工作。同时,“0”信号经ICA反相后使ICB的⑤脚为“1”,“0”振荡器起振,产生较低频率(以200Hz~600Hz为宜)的矩形波振荡信号,通过ICD驱动HTD发出低频鸣响;(3)当探针T检测到“1”时间,经ICA反相使ICB的⑤脚为“0”,“0”振荡器不工作,此时VT导通,Icc的⑦脚为“1”,“1”振荡器起振。以1000Hz-1500Hz为宜的振荡信号,经ICD驱动HTD发出高频鸣响:(4)当探针T检测到“CP”脉冲时,相当于“0”、“1”交替输入,“0”振荡器和“1”振荡器轮流输出,HTD产生高、低频率的混合鸣响。 元件选用:ICA—ICD选用带施密特触发器的二输入端与非门集成电路CD4093,其内含有4个二输入端与非门,故可满足要求。VT选用3DG8D.取β=80~120,HTD使用27A-1型压电蜂鸣器,图中的+5V、GND分别接被测电路的电源和地。

作者:沈左

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

发布评论请先 登录

相关推荐

时序逻辑电路的基本概念、组成、分类及设计方法

Logic Circuit)是一种在数字电路中,其输出不仅取决于当前输入,还取决于过去输入历史的电路。与组合逻辑电路(Combinational Logic Circuit)不同,组合逻辑

时序逻辑会产生锁存器吗

时序逻辑电路本身并不直接“产生”锁存器,但锁存器是时序逻辑电路中的重要组成部分。时序逻辑电路(Sequential Logic Circuits

数字电路中基本逻辑关系有哪三种

数字电路中的基本逻辑关系主要有三种,它们分别是: 与逻辑(AND Logic) : 定义:当所有输入信号均为逻辑1(高电平)时,输出才为逻辑

opa857在test mode下,out端输出电压不随TEST_IN的电压变化怎么解决?

原理图:

CTRL(增益控制引脚): logic 0–5kΩ

logic 1–20kΩ

OPA857有两种模式:normal mode 和 test mode ,由TEST_

发表于 08-02 07:15

触发器和时序逻辑电路详解

电路(Sequential Logic Circuits)则是由触发器、逻辑门以及可能的时钟信号源组成的电路,它们能够处理随时间变化的输入信号,并产生随时间变化的输出信号。下面将详细探讨触发器和时序

组合逻辑控制器的设计步骤是什么

组合逻辑控制器(Combinatorial Logic Controller)是一种数字电路,用于根据输入信号生成输出信号。它不包含存储元件,因此输出仅取决于当前的输入信号。组合逻辑控制器广泛应用

组合逻辑控制器是什么设备

组合逻辑控制器(Combinatorial Logic Controller,简称CLC)是一种用于控制和管理复杂系统或设备的电子设备。它通常由多个逻辑门、触发器和其他逻辑元件组成,能

组合逻辑控制器的基本概念、实现原理及设计方法

组合逻辑控制器(Combinatorial Logic Controller)是一种在数字电路中实现逻辑功能的设备,它根据输入信号的当前状态来产生输出信号,而不考虑输入信号的历史状态。组合逻辑

组合逻辑控制器的工作原理是什么

组合逻辑控制器(Combinatorial Logic Controller,简称CLC)是一种常见的数字电路设计,广泛应用于计算机、通信、控制等领域。本文将详细介绍组合逻辑控制器的工作原理,包括其

如何实现PLC的自动化控制逻辑

在工业自动化领域,PLC(Programmable Logic Controller,可编程逻辑控制器)扮演着至关重要的角色。PLC通过编程实现自动化控制逻辑,使设备能够按照预定的程序进行工作,极大

keil中Logic Analyzer可以在硬件上在线调试,为什么把全局变量加入Logic Analyzer不显示波形呢?

keil中Logic Analyzer可以在硬件上在线调试,按照说明文档上调试,用的是SW模式,为什么把全局变量加入Logic Analyzer不显示波形呢?是不是时钟频率选择的不合适?还是必须得对调试寄存器配置?

发表于 05-16 06:47

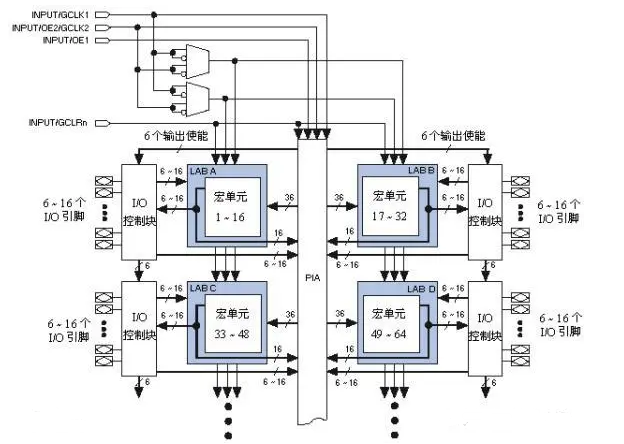

CPLD组成和逻辑块作用介绍

在CPLD(Complex Programmable Logic Device,复杂可编程逻辑器件)中,逻辑块是实现逻辑功能的核心模块。它主要由可编程乘积项阵列(即与阵列)、乘积项分配

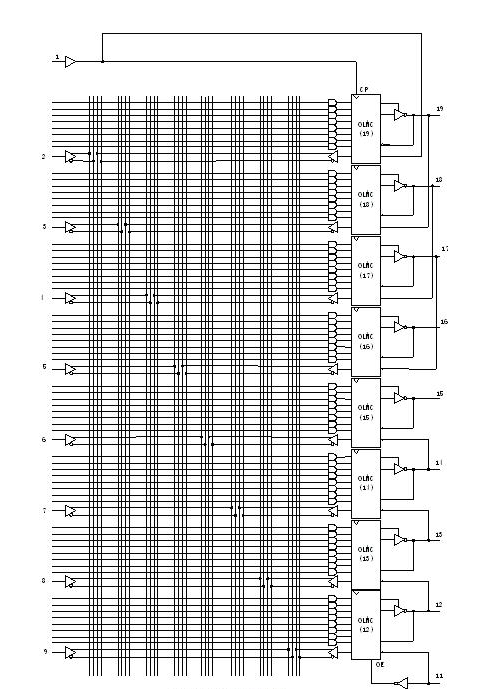

通用阵列逻辑(GAL)电路结构设计分析

通用阵列逻辑(GAL)是一种可编程逻辑器件,由Lattice公司在PAL(可编程阵列逻辑)的基础上设计出来。GAL采用可编程的输出逻辑宏单元OLMC(Output

发表于 02-02 12:21

•2041次阅读

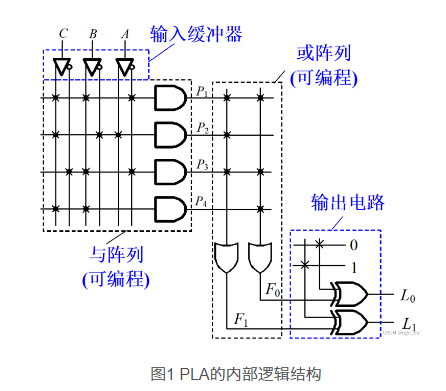

可编程逻辑阵列PLA内部逻辑结构示意

可编程逻辑阵列(Programmable Logic Array,PLA)和可编程阵列逻辑(Programmable Array Logic,PAL)都是数字

发表于 02-02 11:41

•2894次阅读

频率逻辑笔,Logic test circuits

频率逻辑笔,Logic test circuits

评论