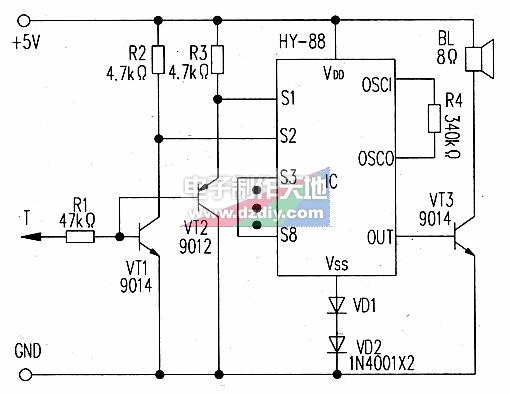

关键字:逻辑测试电路图,HY88

电路原理:电路中.HY-88是一片采用PCB(印刷线路板式软封装)封装的8声效音乐集成电路,它有s1~s8共8个触发控制端,低电平触发有效,对应着内部ROM(只读存储器)预先存储的8种动物叫声,分别是虫叫、蟋蟀、青蛙、布谷鸟、猫、狗、牛及马蹄声。调整振荡电阻R4可改变叫声音调,音频信号经VT3放大后驱动扬声器BL发声。VD1、VD2是降压二极,以使其Vdd,Vss间的工作电压符合2.5V~4.5V范围要求。该逻辑笔的检测状态为:(1)当探针T未接触电路或检测到“悬空”时,VT1和VT2均截止,Ic的触发端s1、s2分别被R3、R2上拉为“1”,IC不工作,BL无声;(2)当探针T检测到“O”时,VT1截止,VT2导通,s2为“1”,s1被“0”触发,BL发出虫鸣声;(3)当探针T检测到“1”时,VT1导通,VT2截止,S1为“1”,S2被“0”触发,BL发出蟋蟀叫声;(4)当探针T检测到“CP”脉冲时,、VT1、VT2轮流导通,s1、S2被交替触发,BL产生蟋蟀和虫两种呜叫声。

作者:沈左

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

发布评论请先 登录

相关推荐

西门子推出Tessent In-System Test软件

西门子数字化工业软件日前推出 Tessent In-System Test 软件,作为一款突破性的可测试性设计(DFT)解决方案,旨在增强下一代集成电路(IC)的系统内测试能力。

时序逻辑电路的基本概念、组成、分类及设计方法

Logic Circuit)是一种在数字电路中,其输出不仅取决于当前输入,还取决于过去输入历史的电路。与组合逻辑电路(Combinational Logic Circuit)不同,组合逻辑

时序逻辑会产生锁存器吗

时序逻辑电路本身并不直接“产生”锁存器,但锁存器是时序逻辑电路中的重要组成部分。时序逻辑电路(Sequential Logic Circuits

数字电路中基本逻辑关系有哪三种

数字电路中的基本逻辑关系主要有三种,它们分别是: 与逻辑(AND Logic) : 定义:当所有输入信号均为逻辑1(高电平)时,输出才为逻辑

opa857在test mode下,out端输出电压不随TEST_IN的电压变化怎么解决?

原理图:

CTRL(增益控制引脚): logic 0–5kΩ

logic 1–20kΩ

OPA857有两种模式:normal mode 和 test mode ,由TEST_

发表于 08-02 07:15

触发器和时序逻辑电路详解

电路(Sequential Logic Circuits)则是由触发器、逻辑门以及可能的时钟信号源组成的电路,它们能够处理随时间变化的输入信号,并产生随时间变化的输出信号。下面将详细探讨触发器和时序

multisim中逻辑转换仪怎么用

Multisim是一款由National Instruments公司开发的功能强大的电子设计自动化软件,广泛应用于电子电路设计、仿真和测试领域。逻辑转换仪(Logic Converter

模拟示波器能测试逻辑信号吗

模拟示波器是一种用于测量和显示电压波形的电子测试仪器,它能够测量电压、频率、周期、相位等参数。虽然模拟示波器主要用于测量模拟信号,但在某些情况下,它也可以用于测试逻辑信号。 模拟示波器测试

组合逻辑控制器的设计步骤是什么

组合逻辑控制器(Combinatorial Logic Controller)是一种数字电路,用于根据输入信号生成输出信号。它不包含存储元件,因此输出仅取决于当前的输入信号。组合逻辑控制器广泛应用

组合逻辑控制器是什么设备

组合逻辑控制器(Combinatorial Logic Controller,简称CLC)是一种用于控制和管理复杂系统或设备的电子设备。它通常由多个逻辑门、触发器和其他逻辑元件组成,能

组合逻辑控制器的基本概念、实现原理及设计方法

组合逻辑控制器(Combinatorial Logic Controller)是一种在数字电路中实现逻辑功能的设备,它根据输入信号的当前状态来产生输出信号,而不考虑输入信号的历史状态。组合逻辑

车载T-Box逻辑功能测试方案

北汇信息基于对客户需求规范、行业法规及自身测试经验Know-How,为客户提供完整和专业的T-Box逻辑功能测试解决方案。支持在实验室环境及实车环境下完成T-Box上层逻辑功能

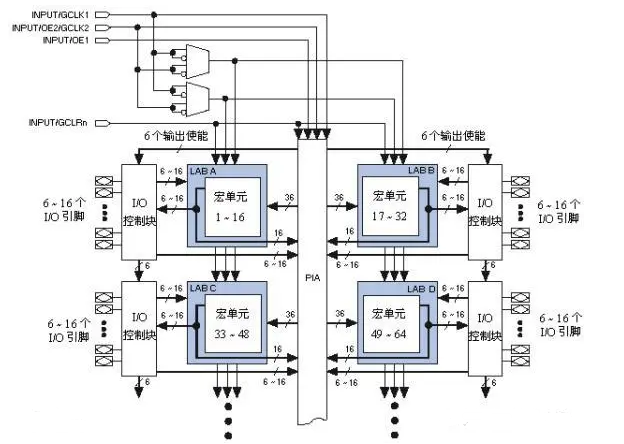

CPLD组成和逻辑块作用介绍

在CPLD(Complex Programmable Logic Device,复杂可编程逻辑器件)中,逻辑块是实现逻辑功能的核心模块。它主要由可编程乘积项阵列(即与阵列)、乘积项分配

音乐逻辑测试笔,Logic test circuits

音乐逻辑测试笔,Logic test circuits

评论