IEEE 1149.1边界扫描测试标准(通常称为JTAG、1149.1或“dot 1”)是一种用来进行复杂IC与电路板上的特性测试的工业标准方法,大多数复杂电子系统都以这种或那种方式用到了IEEE1149.1(JTAG)标准。为了更好地理解这种方法,本文将探讨在不同年代的系统开发与设计中是如何使用JTAG的。

大多数复杂电子系统都以这种或那种方式用到了IEEE1149.1(JTAG)标准。如果系统采用的是复杂FPGA或CPLD,那么几乎可以肯定这些硬件是通过JTAG端口设置的。如果系统利用仿真工具来调试硬件或软件,那么仿真工具也很可能是通过JTAG端口与微处理器对话。而且,如果系统中采用了球栅阵列(BGA)封装的IC,那么JTAG也是测试BGA器件与底层印制电路板之间连接的最有效方法。

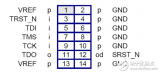

支持EEE 1149.1边界扫描测试标准的IC与电路板都具备一个支持JTAG测试的4线串行总线(第5条线为可选的复位线)TDI(测试数据输入)、TDO(测试数据输出)、TMS(测试模式选择)与TCK(测试时钟)。该总线主要支持对焊点、电路板过孔、短路和开路等连接进行结构测试。此外,许多CPLD和 FPGA制造商也将JTAG作为其器件在系统编程与配置的标准方法。JTAG不但支持结构(互连)测试,如今还是一种用于在系统级实现配置、编程以及混合信号测试的标准方法。

但大多数设计团队都在新设计中对JTAG的应用更倾向于不一步到位,而是以一种更易掌控的方式慢慢转为全面利用JTAG接口。有些团队规则(discipline)中广泛利用了JTAG接口,有些则只利用了其中一部分,但每种规则都根据其自身的需要调整JTAG。在各种规则的共同作用下,发展出了几代不同的JTAG应用,每一代JTAG应用都有各自的特点,具有某种增强功能。

由于存在各种各样的JTAG接入要求,所以开发团队必需采用一种跨规则的JTAG接入策略以最大程度地发挥JTAG接入的功能。这种策略对于实现一种标准方法非常必要,这种标准方法可以复用,并且下一代产品可以基于其构建。为了更好地理解这种方法,我们将探讨在不同年代的系统开发与设计中是如何使用JTAG的,目的是通过借助过去有关JTAG接入的经验或投入,推动设计向新一代发展。

JTAG应用的各个阶段

1、第一代JTAG应用

在JTAG应用的第一阶段,只用到了某些有关电路板的特性和功能,有关该方法的整理和标准化工作却做得很少。

这是一种最简单的方法,几乎甚至完全不需要进行任何软件工具投资,通常使用IC厂商提供的免费工具即可。该阶段的JTAG通常不具备或者只具备很有限的诊断功能,也没有可用于生成测试或编程的矢量的软件。这时的JTAG接入只在生产时用于配置CPLD或对闪存编程。稍复杂一些的板卡也可以用它来做测试。

然而,这并不是成本最低的方法。因为每种规则都有可能会为其自身的需要用一个单独的JTAG接头(header),于是一块电路板上就得用多个JTAG接头,从而增加了成本,也占用了电路板空间。而且,每种规则可能都会开发它们自己的“自制”软件工具和硬件,以实现与JTAG特性的交互, 而这些软件工具和硬件对其他规则(discipline)而言却是多余的。所以,采用这种方法开发的产品受其定制开发的影响,很难转移到新一代的产品中去。如果在生产中采用,这种方法也会增加成本,因为它需要进行多次插入。

许多开发团队都被这一代JTAG应用绑住了手脚。最终,当系统复杂性持续增大时,要保持产品的竞争力,就必需采用一种JTAG接入策略。

2、第二代JTAG应用

在第二代JTAG应用中, 不同的开发团队规则对在新板卡设计上采用JTAG功能进行管理。该阶段的JTAG应用需要一定程度的ATPG(自动测试程序生成)软件工具(这类软件工具具有稳健的诊断功能)投资,用于对编程和测试矢量的开发和传送进行管理。这类ATPG工具的供应商提供从简单的针对每一任务的矢量生成的支持与咨询服务, 也提供生产用的多任务(mulTI-seat)全套软件支持。

在每块电路板上添加一个策略性IC器件——JTAG复用器件,目的是去除电路板上的多个1149.1接头并管理多个JTAG通路。这个JTAG复用器件所占用的电路板空间通常比一个JTAG接头还小,但却简化了元件的隔离,也简化了提高接入效率所需扫描路径的组织。

例如,开发人员可能会希望将不同厂商的FPGA隔离在不同的扫描链中,以便简化利用每个厂商提供的工具接入JTAG的过程。另外,我们可能还希望将微处理器放在一个单独的扫描链中,从而在仿真工具调试软件或在闪存写程序时,最大程度提高微处理器的运行速度。ATPG厂商对这些器件都提供了很 好的支持,因此软件支持通常很简单,直接提供交钥匙的方案。

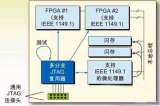

图1 第二代JTAG应用

如今我们的第二代设计都只有一个单独的JTAG接入点,在这种基本配置下,整个板卡的所有仿真、配置和1149.1测试都可以在一次插入中,在一个测试站(test staTIon)上用一个基于PC的系统来实现。

在这一阶段出现了一种新的JTAG总线应用——在产品的整个生命周期中都能利用JTAG接入功能。例如,可以将整个电路板级的矢量图 (vector image)存档,以便在需要现场服务时,对板卡重新编程或调试。同样的接入功能还可以用于现场FPGA固件升级,或用于诊断一个FRU(现场可替换单 元)中的问题。返回厂家进行故障分析的设备也可以利用同一组矢量图(以及厂家或开发测试站)来对问题进行隔离。

如果说这一代JTAG应用有什么缺点,那就是开发团队通常还抱着单一板卡的心态。这是一种常有的心态,认为设计团队的责任只局限于其设计的板卡及其接口。然而,如果不能向第三代JTAG发展,那么这种JTAG应用就出现了瓶颈,限制了使用JTAG实现多板卡的能力。

3、第三代JTAG应用

当能够对一个背板上的多板卡系统级使用到JTAG的特性时,就实现了下一代JTAG接入。在这种环境下,仍然能够单独实现单板卡级JTAG功能,而且还可以利用到板卡间的功能。这一代JTAG应用不 但促进了单板卡上不同规则的设计团队相互合作,也促进了整个系统下不同板卡设计团队之间的合作。如果在上一代JTAG应用中采用了一个JTAG多路器,那 么这个多路器支持多支路(mulTI-drop)接入。采用一种寻址方案,可以将串行JTAG总线用于多支路配置,提供对多板卡的支持。而一旦JTAG能 够接入一块背板上的多个板卡,就能实现系统级的配置或编程(例如,JTAG可以并行接入多块板卡)。

图2 第三代JJTAG

如果驱动器/接收器对允许进行JTAG可接入的全速BIST(内建自测),也能测试板卡之间的背板互连,或者可以验证板卡之间的高速 LVDS串行链接,那么就能对板卡间背板互连的完整性进行测试,或者验证板卡间的高速LVDS串行连接。或这些高速互连都是电容性耦合,并且驱动器/接收 器支持,则可以进行IEEE 1149.6测试。

利用与第二代同样的设备——一个基于PC的JTAG站,就能使用所有这些JTAG功能。这个基于PC的JTAG站用作JTAG主控设备,通过一组单独的线路连接到背板上的JTAG接头。这个主控设备负责驱动测试矢量,并管理整个背板上的器件接入JTAG功能。

第三代JTAG应用中添加的一项最有意思的新功能,在系统运行时,通过这个边带(sideband)JTAG通道可以访问整个系统。具备了这一功能,这使得很多系统级功能得以实现,例如在线“健康”状况监测、故障预测、故障检测、故障插入(用于故障转移测试或冗余度测试)以及诊断。

4、第四代JTAG应用

当测试矢量的传送和管理发生在系统内部时,对JTAG的应用就达到了最高级别,即第四代。第四代JTAG应用采用了一个板载JTAG主控制器来驱动背板JTAG总线。同时,还利用板载存储器存储测试矢量,并利用一个微处理器驱动JTAG主控制器。多板卡系统级主控制器可以位于一块单独的板卡上的,也可以在每块板卡上设置一个主控制器以增强控制性能。

到了第四代,所有前面几代JTAG应用的 功能都能通过远程方式实现,包括编程、配置、互连测试以及诊断,从而极大降低了现场服务与支持所需的成本。当需要升级一个现场系统的固件时,直接将新的配 置文件下载到JTAG主控制器上,再由JTAG主控制器通过背板JTAG总线将其发给目标器件即可。当然,在生产时只要将主控制器禁用,那么仍可使用基于 PC的JTAG接入站,这又进一步增强了灵活性,也在所有集成度上提供了最多的接入选择。

JTAG接入可以通过外部或内部启动,也可以由某些系统事件启动,例如系统上电或电源复位。

小结

迄今为止,JTAG应用与集成中存在的最大障碍,就是如何让人们认识到需要一种基于多个开发规则的策略,并使管理者相信这种策略能够带来经济效益。一旦跨出了这一步,并且采用了 ATPG支持和JTAG复用器件,那么就更容易一步步或一代代地循序渐进评估或实现新的JTAG功能。而且,如果开发团队能够基于先前应用JTAG的经 验,就能更好地发挥JTAG总线的功用。

增大JTAG结构的复杂性并不一定会成为系统的负担,恰恰相反,这样才能完全地发挥JTAG作为一个受到广泛支持的,对现代复杂电子系统进行系统级测试、编程、配置和的健康状态监控的工业标准方法的全部价值。

-

控制器

+关注

关注

112文章

16336浏览量

177826 -

IC

+关注

关注

36文章

5945浏览量

175501 -

JTAG

+关注

关注

6文章

400浏览量

71673

发布评论请先 登录

相关推荐

浅谈嵌入式系统测试JTAG技术各个阶段

基于JTAG的互连测试技术原理分析概述

JTAG先进的功能和系统设计,JTAG Advanced C

什么是jtag接口 jtag接口定义 JTAG ARM

jtag接口是什么_jtag接口定义

JTAG的作用和原理分析

论述学习Linux内核的各个阶段

如何从各个阶段实现控制好回流焊的质量

JTAG(四) 边界扫描测试技术

JTAG与SWD的含义与引脚

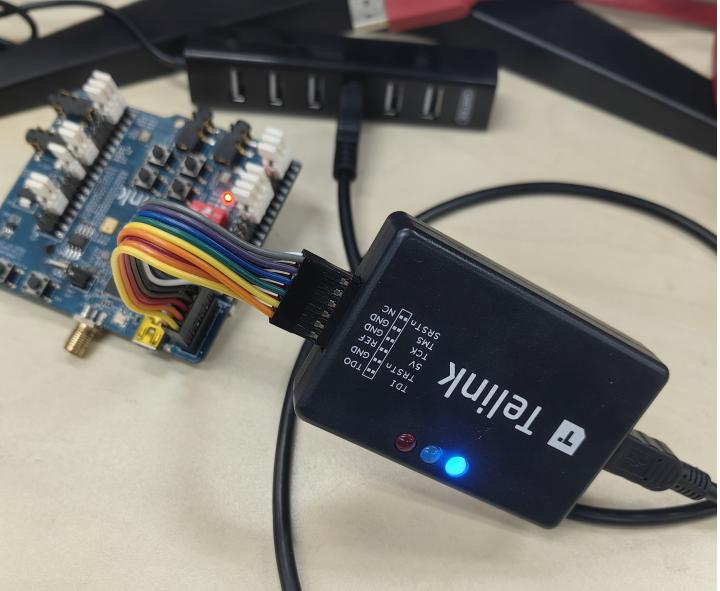

【技术专栏】泰凌微电子JTAG工具使用教程(一)

JTAG技术应用的各个阶段分析

JTAG技术应用的各个阶段分析

评论