采用MAX7348 的串行I2C 总线的键盘电路以及驱动程序的设计,MAX7348 Application

关键字:MAX7348,键盘控制电路

一、简述

本文介绍一种采用MAX7348 的串行I2C 总线的键盘电路以及驱动程序的设计。

I2C 需要连线少,仅需一条串行时钟线和一条串行数据线。允许多主机控制,具有裁决和同步功能,可随意添加或摘除总线上的子器件等诸多优点,所以已经被广泛应用。

二、MAX7348

MAX7348 是美国MAXIM 公司生产的2 线接口、低EMI 键盘开关和发声控制器,可监控多达40 个按键,可对按键去抖并保存在FIFO 中,去抖时间用户可在9 ~ 40ms 之间任意设置,MAX7348 自带的音调发生器在控制器的作用下可自动发出按键声和报警声,在发声期间,输出还可以设置为高电平或低电平,以驱动电子发声器、继电器或指示灯。

1. 引脚图

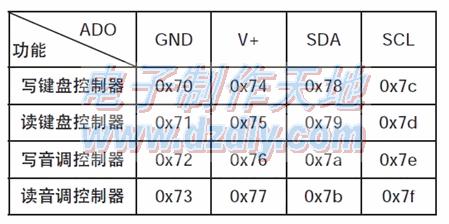

如图1 所示,SDA 、SCL 分别是兼容I2C 串行总线的数据、时钟接口,使用时通常需要接一个典型值为4.7kΩ 的上拉电阻;ROW0 ~ ROW8 为键盘矩阵行输入端口,不用时开路;COL0 ~ COL4为键盘矩阵列输出端口;SOUNDER 为发声器输出端口,该输出为推挽结构,通常与地之间接一个压电陶瓷片或其他发声设备;INT 为中断输出端口;AD0 为地址输入端口,用来设置器件的从地址,该引脚接GND、V+、SDA、SCL 可形成4 种逻辑组合构成MAX7348 的4 个可选的I2C 地址,如表1 ;GND 为接地端,V+ 接电源(2.4 ~ 3.6V)。

表1 2线接口地址分配表

2. 主要内部寄存器

(1) 按键FIFO 寄存器(00H) 该寄存器包含与按键FIFO 状态有关的信息,以及那些经过去抖的事件信息,该寄存器的D0 ~ D5 位表示按键中的那些键已去抖,D6 指明当前去抖按键是否是FIFO 中的最后一个;D7 位是溢出标志,它表示按键FIFO 是否溢出。读按键扫描FIFO 将清除中断信号,但是只有通过执行足够次数的读操作清空FIFO后才能再次产生中断(INT)信号。

(2)去抖寄存器( 01H) 该寄存器用来设置每一个去抖周期的时间,以及使能和禁用GPO 端口,其中D0 ~ D4 位用来在9 ~ 40ms 范围内设置去抖时间,步长1ms,D5 ~ D7 用来设置使能那一个GPO 端口(表2)。

表2 去抖寄存器设置

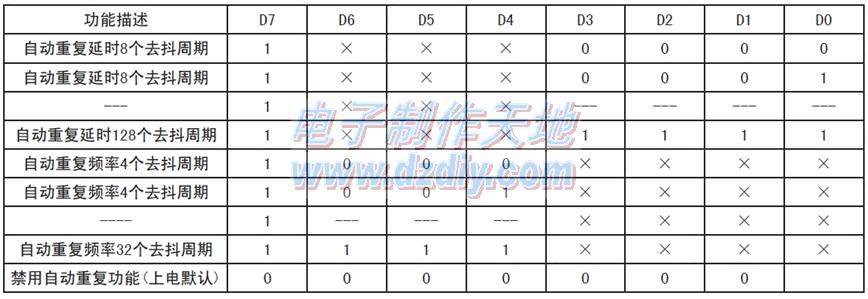

(3)自动重复寄存器( 02H)该寄存器用来设置自动重复频率及其延时。当按键按下且没有释放时,自动重复功能允许连续触发按键事件。自动重复延时规定了第一次按下按键与开始重复之间的时间(如果按键没有释放)。自动重复频率规定了自动重复开始后按键事件连续触发的速度。D0 ~ D3设定自动重复延时,范围从8 个去抖周期到128 个去抖周期。D4 ~ D6 位规定重复频率,范围是4 到32 个去抖周期,D7 位是自动重复功能使能位(如表3 所示)。

表3 自动重复寄存器

(4) 中断寄存器( 03H) 该寄存器包含与中断请求功能设置有关的信息,以及INT 输出的状态,INT 输出也可配置为GPO.中断寄存器是只读寄存器,向该寄存器写入数据无效。

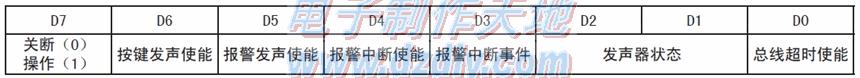

(5)配置寄存器(04H)该寄存器反映发声器的状态、控制I2C 总线超时、使能报警输入中断、使能发声器对报警输入和按键去抖时间做出响应,以及控制器件关断等。该寄存器结构如表4 所示,除D1、D2 设定发声器输出状态外,其余每一位对应一个控制状态,用户可根据需要使能(置"1")或禁止(置"0")。

表4 配置寄存器结构

(6)按键发声寄存器( 06H) 如果配置寄存器(04H)中使能按键发声,那么当一个键或一组键去抖后,发声控制器将发出声音,并由按键发声寄存器设定发声的时间和频率。

除以上几个主要寄存器外还有端口寄存器、报警声寄存器、发声器寄存器等多个寄存器,这些寄存器主要用于控制发声器和扩展GPO 端口,在此不做详细叙述,感兴趣的读者可以自行查阅有关MAX7348 的技术资料。

三、电路设计

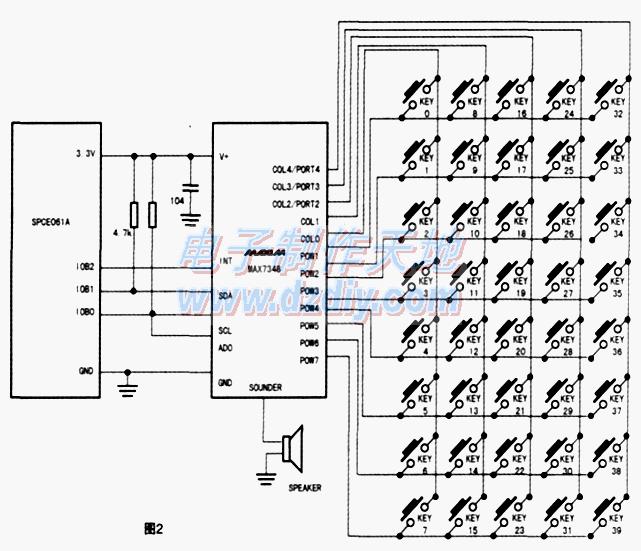

图2 是笔者设计的MAX7348 应用电路,该电路以凌阳(SPCE061A)单片机为主控制器,结合MAX7348 构成了一个具有40 个按键的键盘电路,通过程序可以设置按键发声、自动连续按键、中断输出等功能。MAX7348 的SDA、SCL、INT 分别与SPCE061A 单片机的IOB0、IOB1、IOB2(注:SPCE061A 单片机的IOB2 为外部中断1 的输入口)连接,由于I2C 总线允许挂接多个从机,所以在实际使用中,可以将多个不同从机地址的设备挂接在同一总线上,为单片机节约大量的硬件资源。

四、软件编写

在图2 所示的键盘电路中,由于MAX7348 只具有兼容的I2C 接口,而SPCE061A 单片机本身不具备I2C 接口,要实现二者之间的数据传输,通常采用通用IO 口软件模拟I2C 的方式来实现。图3 是MAX7348 的总线时序。

由图3 所示的时序图可以看出,用软件模拟I2C 总线的传输时序,大致要经历构造开始条件、发送从机地址(含读写标志位)、等待从机响应、发送(或读取)1 个字节数据(或命令)、源程序请从www.ele169.com 下载。

笔者编写的模拟I2C 总线驱动程序,经过多次调试,程序符合I2C 总线传输时序要求,与I2C总线设备通讯可靠,但需要注意的一点是:以上代码是在SPCE061A 单片机默认时钟频率(24M)的情况下编写的,如果采用较高的系统时钟,需要在部分代码中间添加一些延时程序,否则会出现数据丢失,造成通讯错误。

五、小结

本文介绍的MAX7348 与单片机的接口具有电路简单,易于实现,节省了单片机的IO 口,提高了键盘电路的稳定性和可靠性,在笔者制作的5 层电梯模型中工作稳定,性能可靠,是一种值得推广的键盘扩展方案,可应用在工业控制、PDA、医疗器械等多个领域。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

发布评论请先 登录

相关推荐

I2C总线通信原理 如何设计I2C总线电路

I2C总线通信原理 I2C(Inter-Integrated Circuit)总线是一种用于集成电路之间进行通信的

基于I2C总线的智能家居应用

随着科技的飞速发展,智能家居系统已经成为现代生活的一个重要组成部分。I2C(Inter-Integrated Circuit)总线是一种串行通信协议,广泛应用于微控制器和各种传感器之间,因其简单

I2C总线的优缺点分析

I2C总线作为一种广泛使用的串行通信协议,以其简单性和高效性在嵌入式系统中占据着重要地位。 I2C总线的优点 1. 简单性和低成本

I2C总线数据包结构详解

I2C(Inter-Integrated Circuit)总线是一种用于连接微控制器和各种外围设备的通信协议。它使用两条线:串行数据线(SDA)和串行时钟线(SCL),实现了设备之间的

如何选择I2C总线拉电阻

I2C总线是一种广泛使用的串行通信协议,它允许多个设备通过两条线(数据线SDA和时钟线SCL)进行通信。为了确保数据信号的稳定性和减少反射,I2C总

I2C总线与Arduino的接口示例

在现代电子设计中,I2C总线因其简单性和灵活性而广受欢迎。它允许多个设备共享同一通信线路,从而节省空间和成本。Arduino,作为一个多功能的微控制器平台,自然也支持I2C通信。 I2C

I2C总线的工作模式介绍

在现代电子系统中,I2C总线作为一种多主机、多从机的串行通信协议,扮演着至关重要的角色。它允许多个设备共享同一总线,进行数据传输,从而简化了系统设计并降低了成本。

I2C总线故障排除技巧

I2C总线是一种广泛使用的串行通信协议,它允许多个设备在两条线上(数据线SDA和时钟线SCL)进行通信。由于其简单性和灵活性,I2C总线在嵌

I2C总线与单片机的连接

在现代电子系统中,单片机(MCU)是核心控制单元,而I2C总线作为一种多主机、多从机的串行通信协议,因其简单、高效和节省引脚的特性而被广泛应用于各种电子设备中。 I2C

I2C总线设备地址设置方法

I2C总线是一种广泛使用的串行通信协议,它允许多个设备在两条线上(数据线SDA和时钟线SCL)进行通信。每个设备都有一个唯一的地址,以确保数据能够正确地发送到目标设备。 I2C地址概述

I2C总线与SPI总线的比较

在现代电子系统中,微控制器与各种外设之间的通信是必不可少的。I2C和SPI是两种流行的串行通信协议,它们各自具有独特的特点和应用场景。 I2C总线

I2C总线协议的工作原理和寻址格式

I2C(Inter-Integrated Circuit)总线协议,即集成电路总线协议,是一种用于连接微控制器及其外围设备的串行

采用MAX7348 的串行I2C 总线的键盘电路以及驱动程序的设计,MAX7348 Application

采用MAX7348 的串行I2C 总线的键盘电路以及驱动程序的设计,MAX7348 Application

评论