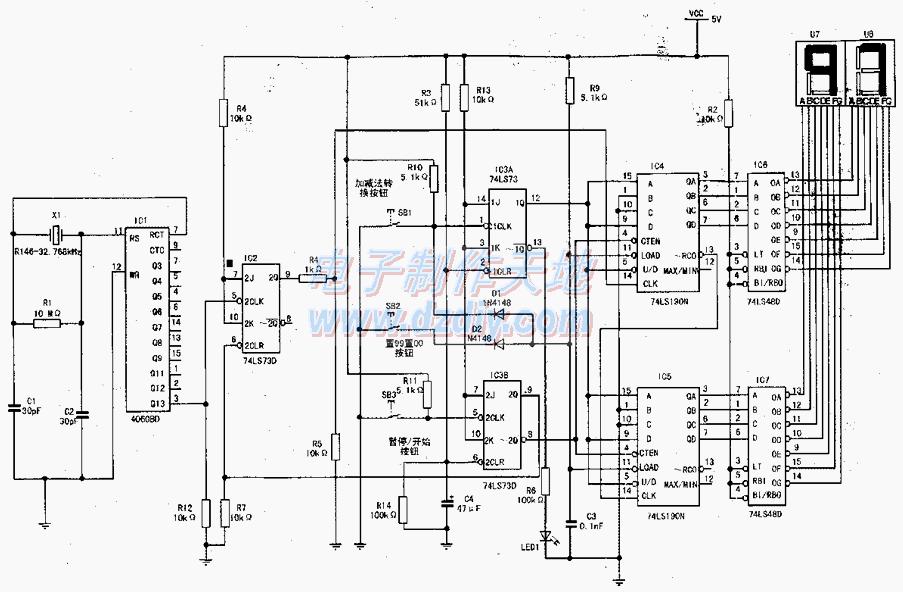

1、振荡与分频:晶振X1与集成电路ICl(4060)内部的非门电路共同产生32768Hz的方波信号,经IC1进行214分频后由IC1的13脚输出频率为2Hz的方波信号,再经IC2(集成触发器74LS73)分频一次,输出1Hz的方波信号作为计数器的计数脉冲,送入到个位计数器IC4进行计数。

振荡电路中的R1为反馈电阻;其数值较大(10MΩ)有利于提高振荡频率的稳定性。电容C1、C2与晶体构成一个谐振型网络,实现对振荡频率的控制,同时提供180度相移,从而和IC1内部的非门构成一个正反馈网络满足振荡条件,使振荡电路正常电工作。

2、计数:计数电路由二块74LS190(IC4、IC5)构成个位和十位的计数。

IC4的13脚为进位输出端/借位输出端)与IC5的14脚(计数脉冲输入端)相连,完成个位向十位进位或借位的功能。

3、译码与显示:该部分电路由两块74LS48(IC6、IC7)和两个数码管组成,IC6对个位计数电路输出的8421BCD码进行译码驱动,数码管显示,IC7对十位计数电路输出8421BCD码进行译码驱动,数码管显示。

4、控制电路:主要由三个按钮SB1、SB2、SB3和一块双JK触发器74LS73构成。

①加法计数控制:接通电源的瞬间,由于电容C4两端的电压不能突变而为0,故IC3A、IC3B的CLR=O,故两触发器清零,即1Q=2Q=O,1Q=2Q=1,2Q=0送到IC2的CLR端,使其清零,此时IC2无计数脉冲输出到计数器74LS190,又因IC3B的Q(的反)=1,该信号送到74LS190的使能控制端(CTEN),则计数器工作在保持状态,故开机后,数码显示不变。再按一次SB2,IC4、IC5的LOAD变为低水平,使IC4、IC5处于并行输入状态,同时因A=D=U/D=0,B=C=0,故IC4、IC5的QA=QB=QC=QD=0,故显示为00(置0),再按一次SB3(启动)使IC3B获得一个下降脉冲,则IC3B输出从O翻转为1,使IC2输出计数脉冲,送至IC4,同时因IC3B的Q(的反)转为0,则IC4、IC5的CTEN=0,此时虽然C4充电后变为高电平,但IC3A无下降脉冲触、发,故其Q保持为0,则U/D=0,故IC4、IC5开始作加法计数。由IC4与IC5的级联关系可知,IC4的进位输出信号作为IC5的计数脉冲,故当个位计数到9时,第十个CP脉冲上升沿到时.RCO/BO有进位脉冲输出到十位,十位开始计数。当计数到99时,第100个脉冲到时,数码显示为00,完成一次100进制加法计数功能。

计数过程中,若要停止计数,再按一下SB3,使IC3B获得一个下降脉冲,其输出端Q翻转为0,Q(的反)=1,则IC4、IC5的CTEN=1,则计数器停止计数而处于保持状态,再SB3-次,又接着计数,实现暂停/开始功能。

②减法计数控制:开机后,因C4作用,IC3A、IC3B、IC2清零,再按一下SB1,D1导通,因C3很小,放电很快,故IC4、IC5的LOAD端变为低电平,则它们处于并行输入状态,同时IC3A被触发,Q由0变1,则A=D=U/D=1,B=C=0(接地),故QAQBQCQD=1001,该数码经译码驱动,显示99(置9),再按一次SB3(启动减法计数)IC3B被触发翻转,Q由0变1,IC2工作,输出计数脉冲,Q由1变0,故IC4、IC5的CTEN=0,则计数数开始作减法计数,若需暂停,则按SB3即可。由级联关系可知,IC4的十三脚输出借位脉冲信号。

③加减计数的相互转换控制若原来是作加法计数,要转为减法计数,则按一次SB1,则IC3A的Q端翻转,由0变1,则A=D=U/D=1,且LOAD=0,则数码管重新置99,再按一下SB3,启动减法计数,反之则反。

④保护电路:接入电容C3是为了避免触发器IC3A触发后,因延时翻转,而IC4、IC5的LOAD端的低电平随着按钮复位而很快消失,造成不置00或不置99,接入C3后,在SB1、SB2复位之后,但因C3充电须要一段时间,故使LOAD保持一段低电平,等待IC3A的延时翻转,以防出现竞争冒险。二极管D1、D2起隔离作用,以免按SB1或SB2时相互干扰或集成电路之间相互干扰。

5、指示电路:LED是加减法计数指示灯,当作加法计数时,LED发光,作减法计数时,LED不发光。

主要元件

IC1为一块4060作分频器,IC2、IC3为二块74LS73,IC4、IC5为二块74LS190作计数器,IC6、IC7为二块74LS48译码器,显示为两块共阴极数码管。

由以上分析可知该电路可做加法计数或减法计数,可用于有关数显电路或倒计时场合。通过制作该电路,对热爱数显电路设计与制作有所帮助与提高。

-

计数电路

+关注

关注

0文章

16浏览量

11976

发布评论请先 登录

相关推荐

数字式100进制加减计数电路的工作原理及制作

数字式100进制加减计数电路的工作原理及制作

评论