华为每年至少拿出10亿美元的研发预算,用于与数据中心相关的投入。

2017年9月,华为发布了面向企业、政府的人工智能服务平台华为云EI。今年4月,华为又发布了面向智能终端的人工智能引擎HiAI。

AI再次进入了“收获”的季节。这是60年来全球ICT学术界和工业界长期耕耘,相互合作的成果。如同公元前的轮子和铁,19世纪的铁路和电力,以及20世纪的汽车、电脑、互联网一样,华为认同:人工智能是一组技术集合,是一种新的通用目的技术(GPT)。

华为在AI上的全新战略,包括人工智能芯片、基于芯片赋予技术框架的CANN和训练框架MindSpore、以及ModelArts,华为将其称之为“全栈全场景AI解决方案”。

“之前一直传华为要做AI芯片,这确实是真的。”华为轮值董事长徐直军在今天上海举行的第三届HUAWEI CONNECT 2018(华为全联接大会)上如是说。

徐直军提出了10个人工智能的重要改变方向:模型训练、算力、AI部署、算法、AI自动化、实际应用、模型更新、多技术协同、平台支持、人才获得。这十个改变不是人工智能的全部,但是基础。

基于这十个改变,华为制定了人工智能发展战略:投资基础研究、打造全栈方案、投资开放生态和人才培养、解决方案增强、内部效率提升。

今天发布的华为昇腾910(Ascend 910),是目前全球已发布的单芯片计算密度最大的AI芯片,还有Ascend 310,是目前面向计算场景最强算力的AI SoC。”

具体来看,华为所说的“全栈”包含四个部分:

一是Ascend (昇腾) ,AI IP和芯片,皆是基于达芬奇架构。芯片分为5个系列,Max、Lite、Mini、Tiny、Nano。

二是CANN,全称为Compute Architecture for Neural Networks (为神经网络定制的计算架构) ,是高度自动化的算子开发工具。根据官方数据,CANN可以3倍提升开发效率。除了效率之外,也兼顾算子性能,以适应学术和行业应用的迅猛发展。

三是MindSpore架构,友好地将训练和推理统一起来,集成了各类主流框架 (独立的和协同的) :包括TensorFlow、PyTorch、PaddlePaddle、Keras、ONNX、Caffe、Caffe 2、MXNet等等。这一架构全面适应了端、边、云场景。

四是ModelArts,这是一个机器学习PaaS (平台即服务) ,提供全流程服务、分层分级API,以及预集成方案。用于满足不同开发者的不同需求,促进AI的应用。

此外,徐直军在现场透露,华为昇腾910将在2019年2季度上市。

根据现场的介绍,这款属于Max系列的昇腾910,采用7nm工艺制程,最大功耗为350W。在现场的PPT中,华为将其和谷歌TPU v2、谷歌TPU v3、英伟达 V100进行了对比。“可以达到256个T,比英伟达 V100还要高出1倍!”徐直军说。

华为昇腾芯片910和310都是基于“达芬奇架构”,是一个全新的AI架构。

之前有媒体写到华为有个“达芬奇计划”,是近十年来最重要的一个计划,也是徐直军负责的项目。此次,徐直军做了澄清,他说确实有“达芬奇项目”但没有“达芬奇计划”,除此之外,其他信息外界传递的信息都不是真的。

徐直军表示,自己会关心每个项目,而达芬奇项目是其中之一。

“为什么要构建新架构来支持人工智能芯片,是因为这是基于华为对人工智能的理解,基于端管云对对人工智能的需求自然产生的。”徐直军表示,“寒武纪也很好,但无法支持我们的全场景。”

其表示,华为需要覆盖从云、到边缘、到端到物联网端,需要全新的架构,创造力的架构。

“现在,我们找到了这个架构。我们开创性的达芬奇架构,满足了极致的算力需求和极致的功耗需求,目前我们还没看到市场上有何架构可以实现全覆盖。”徐直军表示。

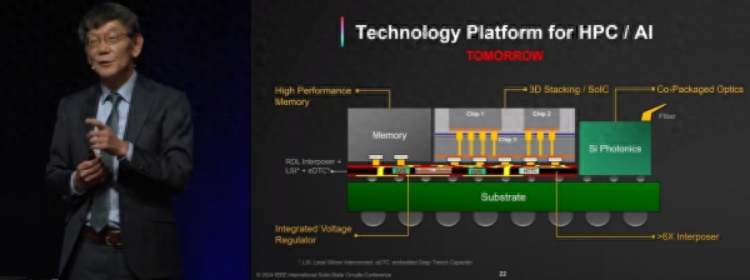

台积电7nm EUV芯片首次流片成功

全球一号代工厂台积电宣布了有关极紫外光刻(EUV)技术的两项重磅突破,一是首次使用7nm EUV工艺完成了客户芯片的流片工作,二是5nm工艺将在2019年4月开始试产。

今年4月开始,台积电第一代7nm工艺(CLN7FF/N7)投入量产,苹果A12、华为麒麟980、高通“骁龙855”、AMD下代锐龙/霄龙等处理器都正在或将会使用它制造,但仍在使用传统的深紫外光刻(DUV)技术。

而接下来的第二代7nm工艺(CLNFF+/N7+),台积电将首次应用EUV,不过仅限四个非关键层,以降低风险、加速投产,也借此熟练掌握ASML的新式光刻机Twinscan NXE。

7nm EVU相比于7nm DUV的具体改进公布得还不多,台积电只说能将晶体管密度提升20%,同等频率下功耗可降低6-12%。

如今在7nm EUV工艺上成功完成流片,证明了新工艺新技术的可靠和成熟,为后续量产打下了坚实基础。

台积电没有透露这次流片成功的芯片来自哪家客户,但是想想各家和台积电的合作关系,其实不难猜测。

7nm之后,台积电下一站将是5nm(CLN5FF/N5),将在多达14个层上应用EUV,首次全面普及,号称可比初代7nm工艺晶体管密度提升80%从而将芯片面积缩小45%,还可以同功耗频率提升15%,同频功耗降低20%。

2019年4月,台积电的5nm EUV工艺将开始风险性试产,量产则有望在2020年第二季度开始,正好满足后年底各家旗舰新平台。

台积电5nm工艺的EDA设计工具将在今年11月提供,因此部分客户应该已经开始基于新工艺开发芯片了。

随着半导体工艺的急剧复杂化,不仅开发量产新工艺的成本大幅增加,开发相应芯片也越来越费钱,目前估计平均得花费1.5亿美元,5nm时代可能要2-2.5亿美元。

PS:Intel刚发布的秋季桌面平台仍然都是14nm,而拖延已久的10nm要到明年才能量产,7nm则是遥遥无期,5nm就更别提了。

-

台积电

+关注

关注

44文章

5651浏览量

166675 -

华为

+关注

关注

216文章

34479浏览量

252145 -

AI芯片

+关注

关注

17文章

1894浏览量

35102

发布评论请先 登录

相关推荐

性能杀手锏!台积电3nm工艺迭代,新一代手机芯片交战

今日看点丨 传苹果2025年采用自研Wi-Fi芯片 台积电7nm制造;富士胶片开始销售用于半导体EUV光刻的材料

谷歌Tensor G5芯片转投台积电3nm与InFO封装

台积电产能分化:6/7nm降价应对低利用率,3/5nm涨价因供不应求

今日看点丨消息称蔚来、小鹏等自研智驾芯片将流片;中国移动超级SIM芯片和MCU芯片采用PUF技术

InspireSemi Thunderbird I 芯片流片,包含 1536 个 RISC-V 核心

华为AI芯片计算密度全球最大 台积电7nm EUV芯片流片成功

华为AI芯片计算密度全球最大 台积电7nm EUV芯片流片成功

评论