在设计中,所有的算数运算符都是按照无符号数进行的。如果要完成有符号数计算,对于加、减操作通过补码处理即可用无符号加法完成。对于乘法操作,无符号数直接采用“*”运算符,有符号数运算可通过定义输出为 signed 来处理。

通过“*”运算符完成有符号数的乘法运算。

module ceshi (out, clk, a, b);

output [15:0] out;

input clk;

//通过 signed 关键字定义输入端口的数据类型为有符号数

input signed [7:0] a;

input signed [7:0] b;

//通过 signed 关键字定义寄存器的数据类型为有符号数

reg signed [7:0] a_reg;

reg signed [7:0] b_reg;

reg signed [15:0] out;

wire signed [15:0] mult_out;

//调用*运算符完成有符号数乘法

assign mult_out = a_reg * b_reg;

always@(posedge clk)

begin

a_reg <= a;

b_reg <= b;

out <= mult_out;

end

endmodule

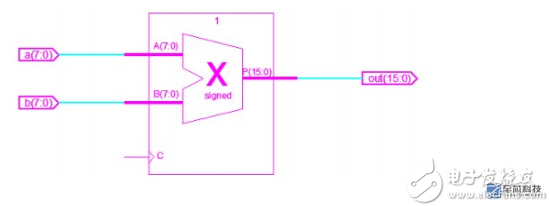

上述程序在 ISE 中的综合结果如下图所示,从其 RTL 结构图可以看到乘法器标注为“signed” ,为有符号数乘法器。

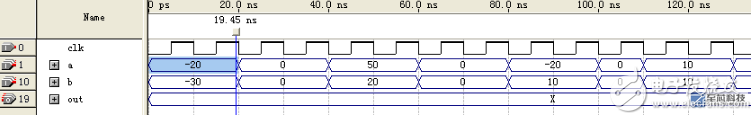

仿真结果图

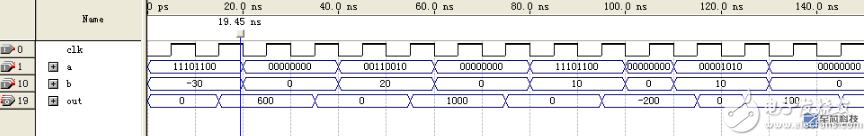

二进制显示的结果

-

FPGA

+关注

关注

1632文章

21816浏览量

607057

发布评论请先 登录

相关推荐

Verilog中signed和$signed()的用法

ADS8688分别设置0 to 1.25 × VREF和±1.25 × VREF采样范围时,得到的16位数据是按照有符号数还是无符号数进行转换?

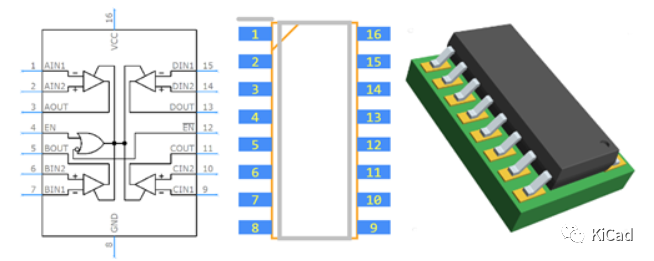

原理图符号和PCB封装有什么不同?

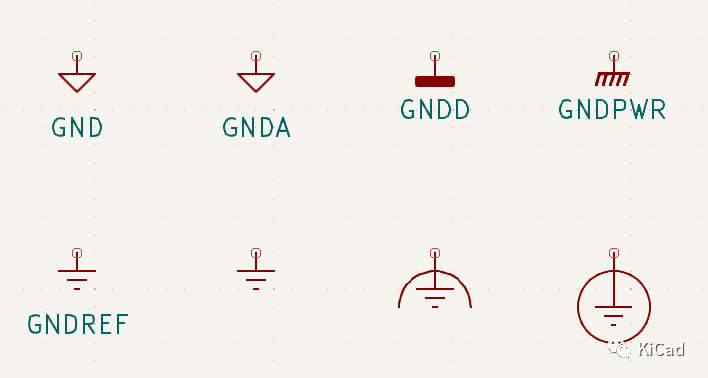

KiCad中不同GND符号的含义及应用

LM70 SPI/MICROWIRE 10位带符号数字温度传感器数据表

什么是一种将模拟信号数字化的技术

LMH6518输出异常的原因?

LM12454/LM12458/LM12H458 12位符号数据采集系统数据表

fpga 有符号数、无符号数

fpga 有符号数、无符号数

评论