ICLR 2019 的论文提交已经截止。根据官方消息,本届大会共收到近 1600 篇投稿,相比 ICLR 2018 的 935 篇,以及 ICLR 2017 的 490 篇,几乎每年都在翻番。

据初步统计,本届 ICLR 论文投稿中最热门的关键词当属强化学习,是 GAN(生成对抗式网络)两倍。强化学习的热度,可见一斑。

其实 ICLR 只算是人工智能领域相对年轻的大会,不过它的来头却不小。2013 年,Yoshua Bengio 和 Yann LeCun 两位大牛牵头,举办了第一届 ICLR 大会,并采取 OpenReview 的公开评审机制。这也是 ICLR 与其他 AI 会议最大的区别。

据雷锋网的介绍,与诸多学术会议通行的单盲、双盲评审制度不同,所有提交的论文都将会公开作者姓名等信息,并且接受所有同行的评价及提问(open peer review),任何学者都可或匿名或实名地评价论文。而在公开评审结束后,论文作者也能够对论文进行调整和修改。

凭借创始人的权威性和透明公开的评审机制,ICLR 受到了学术界的广泛认可,每年的参与人员也越来越多,是深度学习领域的顶级会议之一。

不过,随着这种公开评审的机制受到越来越多的质疑,在去年的时候,ICLR 2018 改成了双盲评审,也就是说,论文作者和评审者都不知道对方的信息。

今年,ICLR 大会又有了新变化。

在担任了 6 年的大会主席(General Chair)之后,Yoshua Bengio 和 Yann LeCun 双双卸任。最新的 ICLR 2019 大会主席是来自 Google 的 Tara Sainath。

根据介绍,Tara Sainath 于 2009 年获得 MIT 电气工程和计算机科学博士学位。在加入 Google 之前,她曾在 IBM Waston 研究中心的语音和语言算法组工作。而且 Tara Sainath 还是 ICLR 2018 的高级程序主席。

ICLR 2019 将于明年 5.6~5.9 在美国的新奥尔良举行。目前,本届大会的所有投稿论文已经可以在 OpenReview.net 上找到,大家可自行查阅。

-

GaN

+关注

关注

19文章

1946浏览量

73671 -

强化学习

+关注

关注

4文章

268浏览量

11266

原文标题:ICLR 2019论文投稿近1600篇,强化学习最热门

文章出处:【微信号:rgznai100,微信公众号:rgznai100】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

大臂展、大负载、具身智能……大族机器人2024年度关键词回顾

中国信通院魏亮:2024人工智能产业十大关键词解读

2024年半导体IPO:关键词是什么?

蚂蚁集团收购边塞科技,吴翼出任强化学习实验室首席科学家

如何使用 PyTorch 进行强化学习

谷歌AlphaChip强化学习工具发布,联发科天玑芯片率先采用

浅析2024年半导体行业的两大关键词

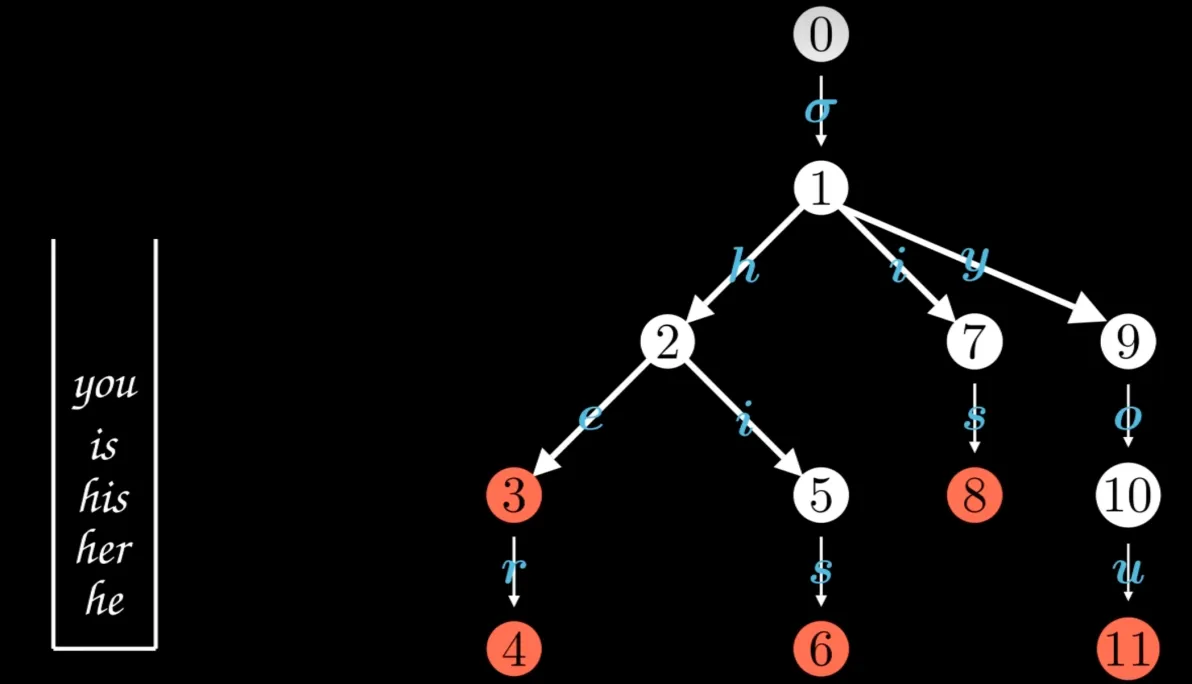

探索AC自动机:多关键词搜索的原理与应用案例

中国信通院发布“2024云计算十大关键词”

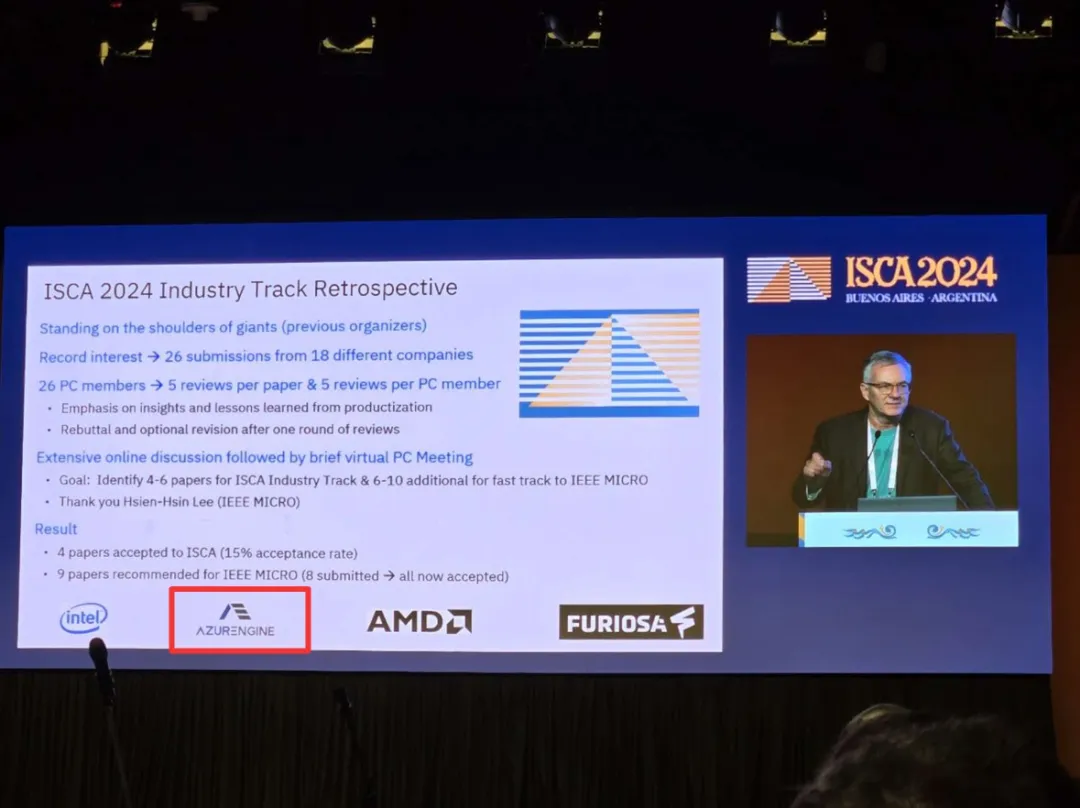

芯动力科技论文入选ISCA 2024,与国际巨头同台交流研究成果

全网热搜的关键词,芯讯通也被@了

微软Edge浏览器将引入PDF阅读器,实现关键词自动生成功能

一文详解Transformer神经网络模型

深开鸿用三个关键词,为你解读《2023 OpenHarmony 年度运营报告》

本届ICLR论文投稿中最热门的关键词当属强化学习

本届ICLR论文投稿中最热门的关键词当属强化学习

评论