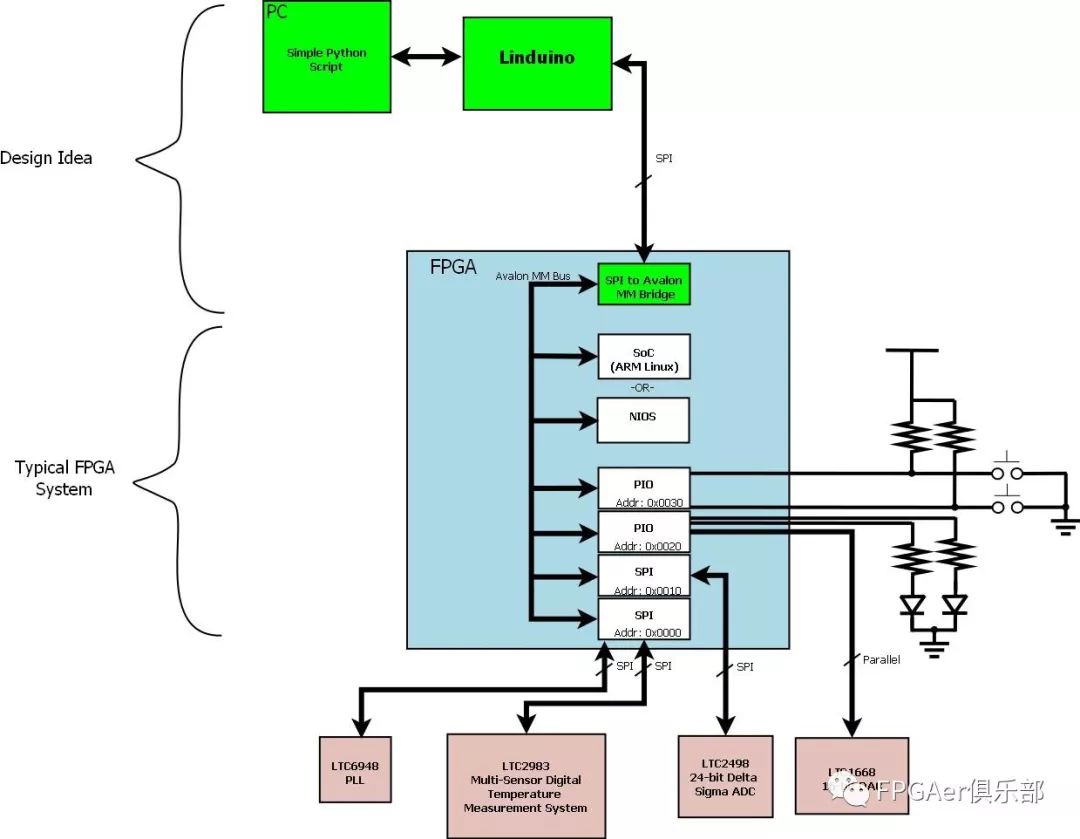

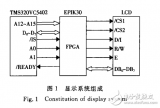

许多新式 FPGA 设计采用了一些用于控制的嵌入式处理器。一种典型解决方案需要使用诸如 NIOS 等嵌入式软处理器。另一种解决方案则使用包含一个内置硬处理器的 SoC 器件。图 1 示出了一个典型的 Altera FPGA 系统,该系统包含处理器和一系列通过 Avalon 内存映射 (MM) 总线连接的外设。这些处理器极大地简化了最终应用,但是要求开发人员拥有坚实的编程背景和精细复杂工具链的相关知识。这会阻碍调试工作的推进,特别是如果硬件工程师需要一种不会烦扰软件工程师即可完成外设读写的简单方法。

图 1:通过 Avalon 内存映射 (MM) 总线连接的典型 Altera FPGA 系统

该设计思想运用了 Altera 的 SPI 从端至 Avalon MM 桥接器,以提供一种跳上 Avalon 总线的简单方法。采用这种方法有两项优势:它并未损害原始系统设计,而且该桥接器能够与嵌入式处理器共存。对于图 1 中所示的系统,SPI-Avalon MM 桥接器将允许设计师直接控制 LTC6948 分数 N PLL 的频率,设定 LTC1668 DAC 电压,从 LTC2498 读取一个电压,或者从 LTC2983 读取温度,就像处理器一样。

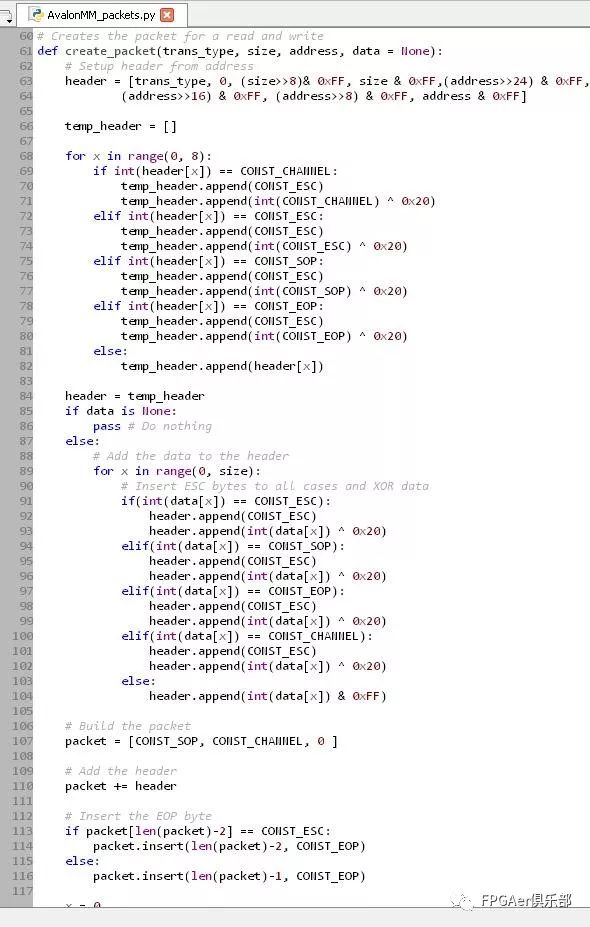

图 2:荧光笔 + 示例代码 + 反向工程 = Python 脚本

Altera 提供了一款针对 SPI-Avalon MM 桥接器的参考设计。不幸的是,文档充其量是稀少的,并且使用一个 NIOS 处理器作为 SPI 主控器。这实际上违背了 SPI 桥接器的初衷,因为 NIOS 处理器可直接连接至 Avalon MM 总线。一款实用的 SPI 主控器是凌力尔特的 Linduino®微控制器,它是具有附加特性的 Arduino 克隆产品,以与 LT 演示板相连接。附加特性之一是电平移位 SPI 端口。当连接至具有低至 1.2V 电压的 FPGA I/O 块时,这种电平移位功能是特别有帮助的。Linduino 固件可用于通过一个虚拟 COM 端口接受命令并把命令转化为 SPI 事务处理。

在对 Altera 实例设计实施了反向工程之后 (图 2 的左侧),开发一个 Python 库以生成桥接器将要接受的数据包。这些数据包随后被转化为 Linduino 命令。这样,一个简单的 Python 脚本使得硬件工程师能够全面地控制项目,并不需要彻底改变接口协议。在 LinearLabTools Python 文件夹中提供了一个控制用于 LTC1668 DAC 的数字图形发生器之频率的 Python 脚本实例,可登录获取。图 3 示出了演示设置。

图 3:DC2459 在工作中

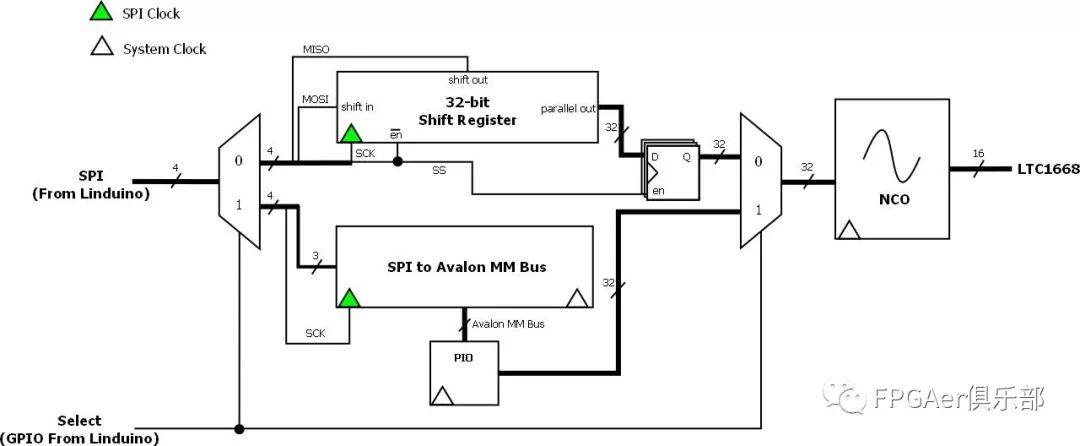

图 4 给出了 FPGA 系统的方框图。请注意,数控振荡器 (DCO) 可由移位寄存器或 PIO 内核来控制。内置移位寄存器用于调试,因为它提供了 NCO 的直接控制。把 GPIO 线逻辑电平设定为“高”将使能 SPI-Avalon MM 桥接器,该桥接器接着通过 Avalon MM 总线控制一个 32 位 PIO 端口。然后,PIO 输出控制 NCO 频率。

图 4:DC2459A FPGA 系统方框图

当最基本的系统运行时,可以把额外的 Avalon 外设 IP 内核连接至 Avalon MM 总线。为了设计系统,Altera 提供了一款被称为 Qsys 的系统集成工具。这款工具提供一个 GUI 以相互连接 IP。Qsys 随后被用于把 GUI 系统转化为硬件描述语言 (HDL) Verilog。图 5 示出了该 GUI。最后,系统将被添加至用于实施的顶层。IP 的地址是完全可配置的。就给出的实例而言,PIO 被设定在一个 0x0 的基地址单元。

图 5:Qsys GUI

一旦在 FPGA 中实现了设计,则 LinearLabTools 中提供的 Python 库包含两个函数以与设计接口:

transaction_write(dc2026, base, write_size, data)

transaction_read(dc2026, base, read_size)

这些函数的第一个参数是 Linduino 串行端口实例。第二个参数是外设在 Avalon 总线上的地址。这些函数分别接受和返还字节列表。编写这两个函数以在读和写 IP 时提供灵活性。如欲设定用于所提供实例的 NCO,则所需的就是 transaction_write 函数。

公式 1 用于确定频率控制字。

公式 1:频率控制字 = (期望的频率/系统时钟频率) x 232

如欲把 NCO 设定至 1kHz 和一个 50Msps 采样速率,则频率控制字数值 = 85899。该数值用十六进制来表示即为 0x00014F8B,其作为一个 4 字节列表进行传递。于是,用于把 DAC 设定至 1kHz 的 Python 代码为:

transaction_write(linduino_serial_instance, 0, 0, [0x0,0x01,0x4F, 0x8B])

注:根据逻辑设计,PIO 的基地址为零。

图 6:Python Avalon 总线示例

提供了一个图 6 所示的简单 Python 脚本,以演示 FPGA 设计和 Python 脚本的接口。它包含一个简单的文本接口以配置 NCO。一个重要提示是 Avalon SPI 桥接器采用 SPI Mode 3。这是痛苦地通过反复试验而确定正确模式;并通过分析 Altera 实例中的 NIOS 处理器 SPI 接口进行验证。

总括来说,该实例项目展示了完全无需“接触”嵌入式处理器便可控制系统的能力。这让硬件工程师不必麻烦软件工程师就能在项目方面取得进展。这种方法的好处可以悄然地添加至 FPGA,并不会影响原始设计。硬件工程师可以把精力集中在硬件上。

-

FPGA

+关注

关注

1664文章

22545浏览量

640413 -

接口

+关注

关注

33文章

9630浏览量

157761

原文标题:通过Altera FPGA系统实现FPGA接口的简化设计

文章出处:【微信号:FPGAer_Club,微信公众号:FPGAer俱乐部】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

如何利用FPGA芯片进行简化的PCI接口逻辑设计?

简化FPGA的电源解决方案

SPI-4.2接口的FPGA实现

基于FPGA 的IDE硬盘接口卡的实现

基于FPGA的IDE硬盘接口卡的实现

IIS接口的FPGA实现

通过Altera FPGA系统实现FPGA接口的简化设计

ARM与FPGA的接口实现的解析

如何实现FPGA接口的简化设计?

如何实现FPGA接口的简化设计?

评论