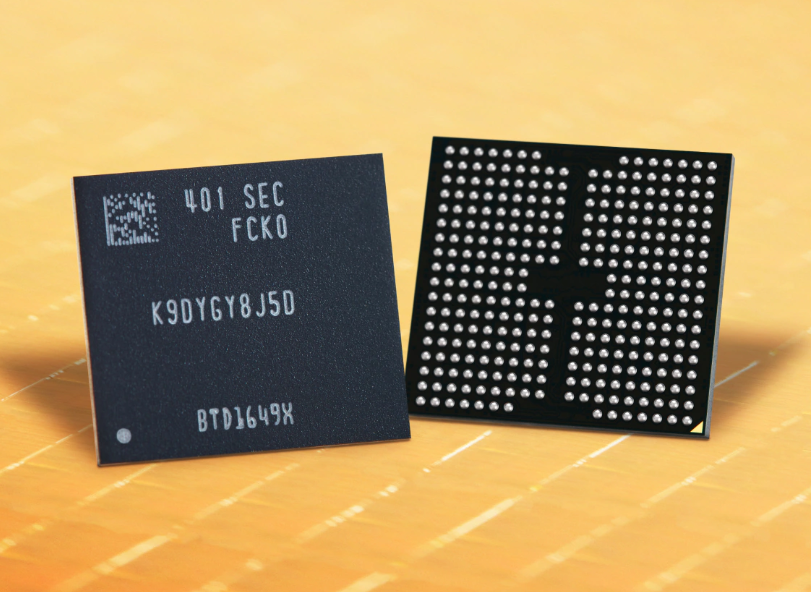

当英特尔在1988年推出第一批NOR芯片时,闪存开始声名鹊起。并且,NOR为三年后的NAND闪存铺平了道路。在所有半导体技术中,NAND的部署速度史无前例,在短短十年内,从18亿美元增长到180亿美元。到2017年,该技术创造500亿美元收入,这是创历史记录,相当于1990年全球半导体市场的总和。NAND闪存无疑是大市场。

但随着业界开发出多种新的存储技术作为潜在替代品,这种局面即将发生改变。

NAND闪存面临限制

在过去40年里,根据摩尔定律,通过平均每年减少30%单个比特的大小,每年或每两年半导体芯片上的晶体管数量翻一番。这反过来又可降低成本,推动芯片更广泛的部署。这种30%的减少被称为工艺缩减,而这种持续的尺寸和成本降低的现象被称为缩放。

大多数半导体都可以持续缩小,但闪存不是这样:在闪存中,位作为电子存储在浮动栅极上,浮动栅极可承载的电子数量与晶体管的大小成正比。在15纳米(nm)工艺几何结构中,1和0之间的差异仅为几十个电子,这在数字芯片内的噪声中极其难以检测。如果制造商将晶体管的尺寸减小30%%,正如他们一直做的那样,那么,电子的数量就会低于可检测的水平。

整个半导体市场一直建立在持续降低成本的期望之上。如果闪存价格不再下降,这显然行不通。面对平面NAND缩放限制,我们应该怎样做来继续降低成本?

3D NAND登场

在2006年,东芝(Toshiba)推出了一个聪明的解决方案。他们不是继续缩小芯片表面的晶体管,而是创建垂直结构并沿着塔璧建造晶体管,类似于城市办公楼墙壁的垂直花园。如果地球表面没有足够的种植面积来种植花园,那么就在建筑物的墙壁种植吧。

即使晶体管无法缩放,通过利用这种方法来增加芯片上的晶体管数量,东芝计划继续降低闪存单元的成本。他们将这种方法称为Bit Cost Scaling,或者说BiCS,这是3D NAND闪存的基础。

BiCS不仅可以继续降低成本,还可支持继续使用NAND闪存,因为3D NAND和平面NAND非常相似,只需很少或者根本不需要重新设计就可互换使用。消费者可能会使用两个USB闪存驱动器,一个采用3D NAND,另一个是平面NAND,但他们无法区分二者。这比其它一些新的存储技术更具优势。 目前业界采用东芝的方法。通过BiCS,通过填充半导体层中的孔,在形成的列中构建位。那问题就变成:我们可以构建多高的垂直位塔?现在还不清楚。

当东芝首次开发BiCS时,人们普遍认为列中位数将受到芯片中层数的限制,以及用于创建列的孔的宽度和深度的限制。制造商不能使这个孔小于20nm,因为一些同心层材料必须涂覆在内部,而这些同心层具有最低厚度要求。同时,深度与垂直层的数量成比例,而这些垂直层也有最低厚度要求。考虑到这些限制,孔的纵横比(深度除以直径)由闪存中的垂直层数决定。

构建3D NAND

3D NAND采用相对简单的方法以将更多晶体管放在芯片上:在侧向构建晶体管,而完全不同于此前的方式。

大多数芯片通过光刻工艺制造。在这里,制造数十亿晶体管的模式被映射到硅晶片表面,通过类似于照片底片被称为mask的方法照射光线,然后处理未曝光的硅片部分。这本质上是一种平面方法;照片总是二维的。

那么,我们如何将其转变为3D?在创建3D NAND时,创造者意识到他们可通过另一种方法来构建他们需要的高度重复的模式。如果他们在芯片表面制造很多层材料,例如夹心蛋糕,然后他们可在所有这些层蚀刻孔。这产生的结构类似于在孔壁侧面打印照片。同时,这不需要采用照相过程就可完成,因为这种模式已存在于图层中。当然,除此之外还有更多细节,但这基本就是3D NAND的秘密。

40比1的纵横比难以制造,60比1则极具挑战性。但随着层数增加,则需要更高的纵横比。这似乎意味着3D NAND将限制为三代,或者说大约100层,然后它会被新技术取代。

半导体研究人员是非常创新的群体,他们又提出新的想法,被称为字符串堆叠,可支持更高的层数。通过字符串堆叠,可制造一定层数的3D NAND,然后在其上方构建另一组层级。每组新的层,会形成新的孔,但这个孔是通过较少层数来蚀刻,因此其纵横比保持适中。例如,Micron Technology通过32层两次蚀刻来产生当前的64层3D NAND,而不是通过64层来蚀刻具有挑战性的孔。这相当于两个30比1纵横比孔和一个60比1纵横比孔之间的差异。

没有人知道字符串可堆叠多少次会达到极限。普遍的观点是500层限制,但这无法确定。在半导体世界中,常识通常被证明是错误的。

现在的64层芯片的密度高达1太字节(128GB),而500层芯片可能可存储几乎10倍多数据。我们当然可以想象太字节芯片。如果太字节芯片构建在500层工艺上,这相当于64层128GB。 字符串堆叠的影响意味着3D NAND可能还会存在很长一段时间时间。

3D XPoint呢?

在2015年,英特尔和Micron推出名为3D XPoint的新型内存。这项新技术承诺提供类似RAM的动态速度,价格点在DRAM和NAND闪存之间。这里的目标是在DRAM主存储和NAND SSD之间提供新的存储层,以提高计算机的性价比。

3D XPoint并不会取代NAND闪存或DRAM,尽管它可能会用于减少系统所需的DRAM数量以达到任何给定的性能水平。这完全不同于很多新存储技术,因为很多新存储技术旨在取代闪存或DRAM—当达到扩展限制时。

到目前为止,3D XPoint只能在PCIe非易失性存储器快速(NVMe)接口中使用。虽然NVMe是SSD最快的接口,但与3D XPoint内存的固有速度相比,它速度仍然较慢。事实上,虽然英特尔和Micron公司认为3D XPoint的速度是NAND闪存的1000倍,但事实上,英特尔Optane固态硬盘的速度只有NAND闪存的六到八倍。

显然,这里需要DIMM接口来释放3D XPoint的速度以及充分利用其性价比优势。英特尔承诺以DIMM格式发布3D XPoint内存,但他们尚未公开推出这样的产品。不过,英特尔透露,他们已经在2018年8月的闪存峰会上向谷歌提供这些DIMM。

Objective Analysis的2015年3D XPoint报告预测,3D XPoint内存最重要的市场是用于服务器的DIMM。我们也认同这一结论。现在的3D XPoint内存市场规模相对较小,主要包括愿意花费大量资金来小范围提升性能的客户。

英特尔的3D XPoint战略

让英特尔头痛的是,3D XPoint市场规模仍然很小,这让他们无法将该产品大批量生产。如果没有高产量,其生产成本将会保持很高,可能高于DRAM。然而,英特尔必须以低于DRAM的价格出售3D XPoint,才会吸引消费者。这意味着英特尔必须赔钱来建立市场。

这种方法可能不会吸引其他公司,但对于英特尔来说则不同。3D XPoint内存使该公司可销售价格更高的处理器,以帮助他们赚回在3D XPoint销售中损失的资金。

其他新兴内存技术

3D XPoint只是众多正在研发的新内存技术之一。有些内存技术已经开发相当长的时间,例如相变存储器(PCM),英特尔的Gordon Moore早在1970年就写过相关文章。

这些新技术可实现高性能、低功耗、非易失性以及最重要的是,超越DRAM和NAND闪存的扩展限制。但NAND闪存和DRAM开发商仍在继续想办法绕过障碍,从而推迟新技术取代NAND和DRAM的时间。

嵌入式存储市场最有可能成为这些新技术的温床。但这些新技术可能需要很长时间才有机会取代DRAM或者NAND闪存。嵌入式内存将更快采用新技术,因为逻辑芯片上的内存必须简单且经济地用于制造ASIC、微控制器和微处理器。

NOR闪存是这些芯片上最常见的非易失性内存,它难以扩展超过45纳米,虽然实验室原型可达到最低14纳米。同样的,即使是静态RAM也很麻烦,SPAM位的大小无法成比例地缩放。这可能导致芯片的SPAM部分膨胀,并限制成本优势,这是缩放ASIC、微控制器和微处理器到更小工艺可实现的成本优势。

NOR和SRAM都是是新存储技术可取代的对象,新技术还包括:

磁性RAM(MRAM)是基于磁性技术,目前已经在大批量生产中,用于制造HDD中的磁头。五年来,Everspin Technologies一直在生产这种非易失性技术作为独立内存,并且正在开发嵌入式版本。MRAM是基于类似DRAM的但晶体管单元,使其能够在成本上与DRAM竞争,而不是NAND闪存。

相变内存是英特尔和Micron的3D XPoint内存的基础。大约在10年前,它作为NOR闪存的替代品投入生产,但只有英特尔、三星和STMicroelectronics推出该技术,现在这些厂商已经放弃该产品。

铁电RAM(FRAM)已经投入生产长达20多年,但由于它依赖铅材料而破坏底层硅的完整性,因而人们对其认可度有限。尽管如此,富士通生产的基于FRAM芯片几乎超过所有替代内存替代品的总和。新的研究已经确定一种更友好和更好理解的材料:氧化铪,可作为铁电层,使得人们重新关注这项技术。

导电桥接RAM(CBRAM)是基于通过硫系玻璃对金属丝的迁移。Adesto Technology是唯一一家提供这种内存类型的公司。

电阻式RAM(ReRAM)采用一种类似的技术,其中纳米金属丝通过硫系玻璃层生长。ReRAM开发了一种位单元,其中包含内部选择器机制,可简化生产过程,同时无需开发单独的选择器。

耗氧RAM(OxRAM)是基于类似CBRAM的现象,其中氧离子从硫系玻璃中移除以形成导电通路。该技术尚未投入生产。惠普企业计划在其高级计算机The Machine中使用OxRAM,但这种方法(被称为Memristor)被推迟到最近。

Nanotube RAM, or NRAM,by Nantero is based on a layer of carbon nanotubes that can be electrically compressed or expanded to create a high- or low-resistance state.

纳米管RAM或者NRAM是基于碳纳米管层的技术,它可被电力压缩或扩展以产生高阻抗或低阻抗状态。

除MRAM外,所有这些技术都是基于双端选择器。这些选择器支持微小的单元尺寸–4f²,或者是光学印刷在芯片的最小特征尺寸的四倍。它们也可采用3D XPoint内存类似的方法进行堆叠以降低成本。

直到最近研究才发现,我们可利用氧化铪来制造FRAM,所有上述技术都需要使用新材料,这些材料并不像硅那么好理解。这无疑阻碍这些新技术的部署,因为这些新材料可能会阻碍大规模生产。

成本是阻止这些技术取代现有内存技术的最重要因素。所有这些存储技术都比DRAM或NAND闪存贵几个数量级,使它们只能用于小众应用。FRAM,可在低功耗下快速写入的技术。而MRAM,可快速写入并具有非易失性,而无需不可靠的电池。PCM因其高辐射耐受性而被选用于卫星,而CBRAM出于类似的原因,用于高剂量X射线灭菌的外科手术器械中。

在这些技术投入批量生产前,没有哪项技术可实现低成本以取代现有内存技术。除非有市场,否则不会大量生产,而在价格下降之前市场不会发展。这是鸡与鸡蛋的关系。

展望未来十年

至少在未来十年,NAND闪存仍然将占主导地位,随后是DRAM。如果英特尔实现其3D XPoint目标,那么它将投入批量生产—尽管英特尔最初将赔钱赚吆喝。在短期内,其他新内存技术将作为片上内存获得成功,但它们将在相当长的时间内无法与独立的DRAM和NAND闪存芯片相竞争。邹铮翻译

-

半导体

+关注

关注

334文章

27269浏览量

217961 -

NAND

+关注

关注

16文章

1681浏览量

136109 -

晶体管

+关注

关注

77文章

9681浏览量

138055

原文标题:新存储技术挑战NAND闪存主导地位

文章出处:【微信号:D1Net11,微信公众号:存储D1net】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

英特尔考虑出售Altera股权

英特尔至强品牌新战略发布

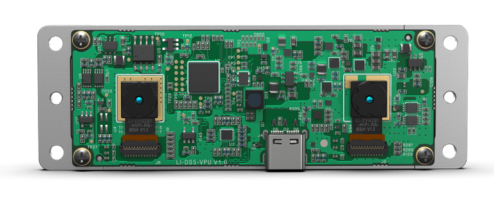

英特尔推出全新实感深度相机模组D421

立体视觉新手必看:英特尔® 实感™ D421深度相机模组

曝Apollo拟向英特尔投资50亿美元

英特尔IT的发展现状和创新动向

3D NAND闪存来到290层,400层+不远了

NAND闪存面临限制,英特尔的3D XPoint战略

NAND闪存面临限制,英特尔的3D XPoint战略

评论