通常,我们优先解决建立时间违例。Setup slack与逻辑延迟、布线延迟、时钟歪斜和时钟不确定性有关。因此,首先要明确这几个因素中哪个因素对建立时间违例起关键作用。具体的衡量标准可由如下几个数值确定。这也是ug1292第三页的主题。

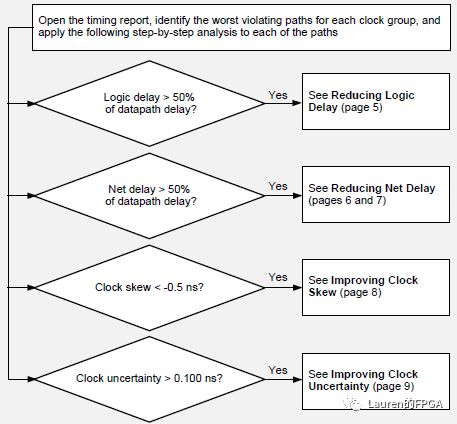

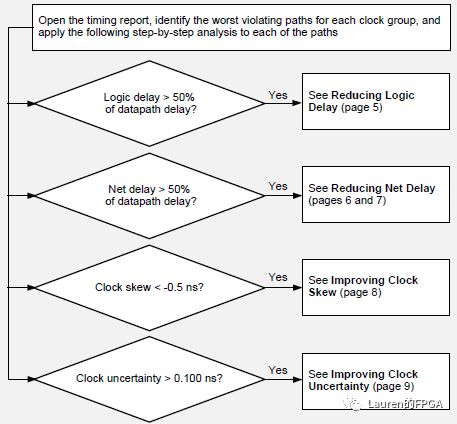

ug1292第三页也给出了建立时间违例分析流程,如下图所示。当逻辑延迟占比超过50%时,要着重降低逻辑延迟;当布线延迟占比超过50%时,要把焦点放在布线延迟上;同时,也要关注一下时钟歪斜和时钟不确定性。当时钟歪斜小于-0.5ns或时钟不确定性大于0.1ns时,两者将成为时钟违例的主要“贡献者”。

图片来源, page 3, ug1292

上述四个数值,无论是在timing report(通过report_timing_summary生成)还是design analysis report(通过report_design_analysis生成)中都有所体现。以timingreport为例,如下图所示,可清晰地显示上述四个数值。

图片来源, page 3, ug1292

注:上述数据只针对UltraScale系列芯片。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

原文标题:深度解析ug1292(3)

文章出处:【微信号:Lauren_FPGA,微信公众号:FPGA技术驿站】欢迎添加关注!文章转载请注明出处。

相关推荐

静态时序分析包括建立时间分析和保持时间分析。建立时间设置不正确可以通过降低芯片工作频率解决,保持

![的头像]() 发表于

发表于 08-22 10:38

•4274次阅读

建立时间(setup time)和保持时间(hold time)是时序分析中最重要的概念之一,深入理解建立时间和保持时间是进行时序

发表于 06-21 10:44

•1752次阅读

有没有人遇到在DC综合后分析建立时间时序,关键路径时序违例是因为起始点是在时钟的下降沿开始驱动的,但是设计中都是时钟上升沿触发的。在线等待各位大牛解惑!很急 求大神帮忙!

发表于 01-04 15:17

本帖最后由 虎子哥 于 2015-3-12 21:24 编辑

建立时间(Setup Time):是指在触发器的时钟信号上升沿到来以前,数据稳定不变的时间,如果建立时间不够,数据将不能在这个时钟

发表于 03-10 23:19

ADC时延和建立时间的区别是什么?以及ADC时延和建立时间将会如何影响您的应用电路?

发表于 04-12 07:19

该文简要讨论了环路性能(建立时间,相位噪声和杂散信号)和环路参数(带宽,相位裕度等)的相互关系。提出并分析了一种自适应的具有快速建立时间的锁相环结构及其关键模块(鉴相

发表于 04-23 08:33

•20次下载

时延和建立时间setup在ADC电路中的区别:对于大多数 ADC 用户来说,“时延”和“建立时间”这两个术语有时可以互换。但对于 ADC 设计人员而言,他们非常清楚

发表于 11-22 23:33

•1596次阅读

初始设计检查流程如下图所示。对象是综合后或opt_design阶段生成的dcp。会依次执行三个命令(图中红色标记),生成三个报告:FailFast报告、时序报告和UFDM(UltraFast Design Methodology)报告。

![的头像]() 发表于

发表于 10-12 11:19

•3654次阅读

UG1292第一页是针对综合后或者opt_design阶段的使用说明。vivado的基本流程有5步(其实不同策略可以更多,具体使用方法和好处以后讲),分别是synth_design

![的头像]() 发表于

发表于 10-30 10:25

•3387次阅读

本篇仿真介绍放大器的建立时间,也称为上升时间。它是高速放大电路、或在SARADC驱动电路设计时,需要谨慎评估的参数。

![的头像]() 发表于

发表于 02-15 16:37

•6344次阅读

AN-359:运算放大器的建立时间

发表于 04-29 15:28

•4次下载

本文主要介绍了建立时间和保持时间。

![的头像]() 发表于

发表于 06-21 14:38

•2666次阅读

建立时间和保持时间是SOC设计中的两个重要概念。它们都与时序分析有关,是确保芯片正常工作的关键因素。

![的头像]() 发表于

发表于 08-23 09:44

•984次阅读

信号经过传输线到达接收端之后,就牵涉到建立时间和保持时间这两个时序参数,它们表征了时钟边沿触发前后数据需要在锁存器的输入持续时间,是接收器本身的特性。简而言之,时钟边沿触发前,要求数据必须存在一段

发表于 09-04 15:16

•856次阅读

电子发烧友网站提供《UltraFast设计方法时序收敛快捷参考指南(UG1292).pdf》资料免费下载

发表于 09-15 10:38

•0次下载

深度解析ug1292建立时间违例分析流程

深度解析ug1292建立时间违例分析流程

评论