随着三星宣布7nm EUV工艺的量产,2018年EUV光刻工艺终于商业化了,这是EUV工艺研发三十年来的一个里程碑。不过EUV工艺要想大规模量产还有很多技术挑战,目前的光源功率以及晶圆产能输出还没有达到理想状态,EUV工艺还有很长的路要走。在现有的EUV之外,ASML与IMEC比利时微电子中心还达成了新的合作协议,双方将共同研发新一代EUV光刻机,NA数值孔径从现有的0.33提高到0.5,可以进一步提升光刻工艺的微缩水平,制造出更小的晶体管。

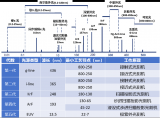

NA数值孔径对光刻机有什么意义?,决定光刻机分辨率的公式如下:

光刻机分辨率=k1*λ/NA

k1是常数,不同的光刻机k1不同,λ指的是光源波长,NA是物镜的数值孔径,所以光刻机的分辨率就取决于光源波长及物镜的数值孔径,波长越短越好,NA越大越好,这样光刻机分辨率就越高,制程工艺越先进。

现在的EUV光刻机使用的是波长13.5nm的极紫外光,而普通的DUV光刻机使用的是193nm的深紫外光,所以升级到EUV光刻机可以大幅提升半导体工艺水平,实现7nm及以下工艺。

但是改变波长之后再进一步提升EUV光刻机的分辨率就要从NA指标上下手了,目前的光刻机使用的还是NA=0.33的物镜系统,下一代的目标就是NA=0.5及以上的光学系统了。

如今ASML与IMEC合作的就是高NA的EUV工艺了,双方将成立一个联合实验室,在EXE:5000型光刻机上使用NA=0.55的光学系统,更高的NA有助于将EVU光源投射到更广阔的晶圆上从而提高半导体工艺分辨率,减少晶体管尺寸。

如今这项研究才刚刚开始,所以新一代EUV光刻工艺问世时间还早,此前ASML投资20亿美元入股蔡司公司,目标就是合作研发NA=0.5的物镜系统,之前公布的量产时间是2024年,这个时间点上半导体公司的制程工艺应该可以到3nm节点了。

-

光刻

+关注

关注

8文章

330浏览量

30321 -

EUV

+关注

关注

8文章

609浏览量

86332

发布评论请先 登录

相关推荐

纳米压印光刻技术旨在与极紫外光刻(EUV)竞争

日本首台EUV光刻机就位

【「大话芯片制造」阅读体验】+芯片制造过程工艺面面观

简述光刻工艺的三个主要步骤

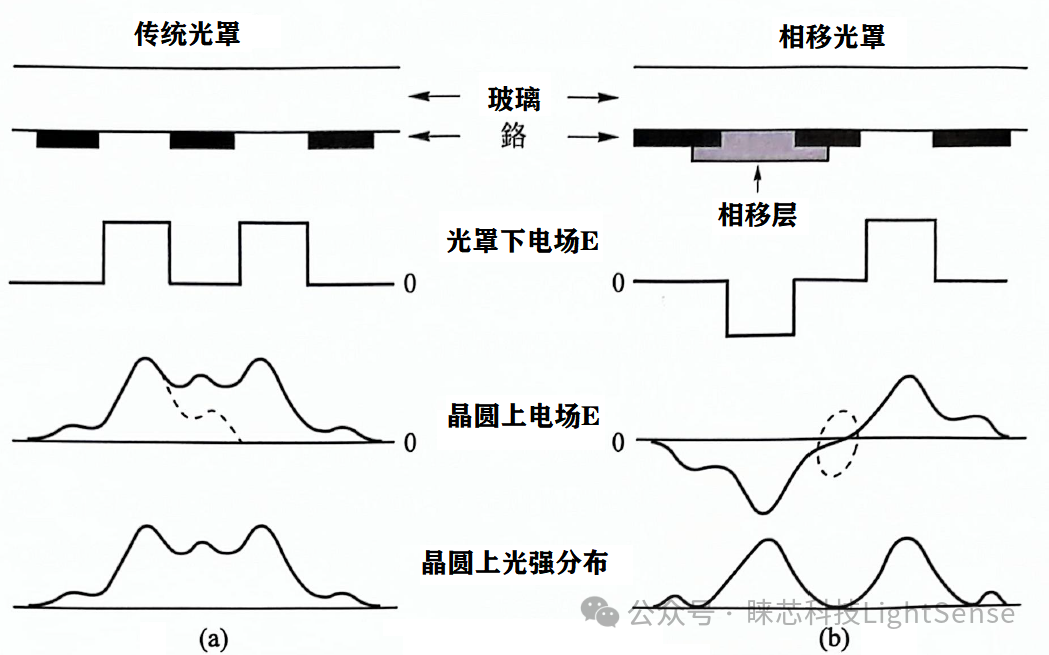

光刻工艺中分辨率增强技术详解

光刻掩膜和光刻模具的关系

光刻工艺的基本知识

日本大学研发出新极紫外(EUV)光刻技术

光刻胶涂覆工艺—旋涂

台积电A16制程采用EUV光刻机,2026年下半年量产

三星拟应用金属氧化物抗蚀剂(MOR)于DRAM EUV光刻工艺

光刻机的发展历程及工艺流程

一文解析半导体设计电路的“光刻工艺”

EUV光刻工艺终于商业化 新一代EUV光刻工艺正在筹备

EUV光刻工艺终于商业化 新一代EUV光刻工艺正在筹备

评论