我们都知道,电路板的叠层安排是对PCB的整个系统设计的基础。叠层设计如有缺陷,将最终影响到整机的emc性能。那么下面就和咱一起来看看到底如何才看懂叠层文件吧~

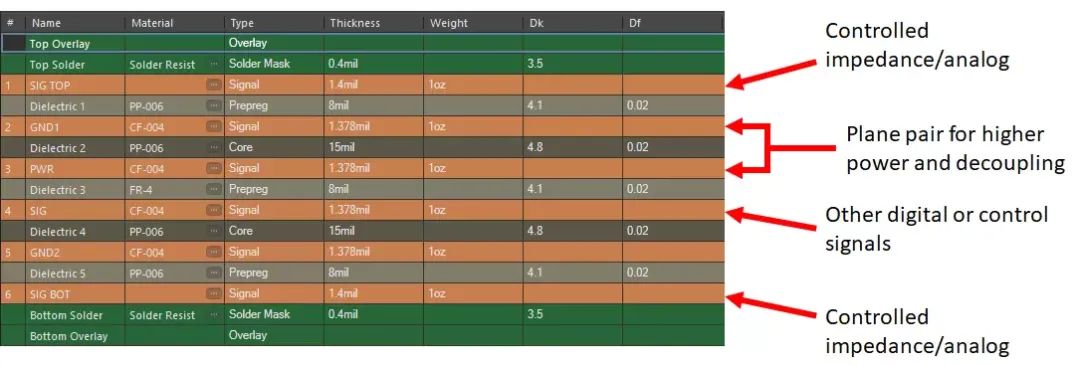

下图是我们一般情况下看到的叠层好的文件图示:

一、对(图一)解析如下:

首先,我们可以看出叠层是8层板,有5个走线层(TOP、ART03、ART04、ART06、BOTTOM),有2个地层(GND02、GND05),有1个电源层(PWR07)。

其次我们可以获得整个板子的使用的PP片情况,GND02-ART03一张芯板(core),ART4-GND05(core) 一张芯板,ART06-PWR07(core) 一张芯板, 其它的用PP加铜箔,最后压合在一起而成的。TOP、GND02层中间的PP片是2116半固化片,ART03、ART04层中间的PP片是由2个3313半固化片和1个7628半固化片压合而成,GND05、ART06层中间的PP片是由2个3313半固化片和1个7628半固化片压合而成,PWR07、BOTTOM层中间的PP片是2116半固化片。

最后,可得知整个板厚为1.6mm(生产时允许有10%公差)。板厚计算如下示:

次外层2116厚度:

实测厚度=理论厚度—铜厚*(1—残铜率)

=0.1174*39.3701mil—1.25*(1—65%)

=4.1845mil

内层3313*2+7628 厚度:

实测厚度=理论厚度—铜厚1*(1—残铜率1)—铜厚2*(1—残铜率2)

=(0.0987*2+0.1933)*39.3701mil—1.25*(1—65%)—1.25*(1—15%)

=13.8819mil

理论板厚:

板厚=内外层铜厚+PP片厚度+芯板厚度

=0.7087*2+1.25*6+4.1845*2+13.8819*2+5.1*3

=60.3502mil

=1.5329mm

二、咱们接着叠层好的文件图二

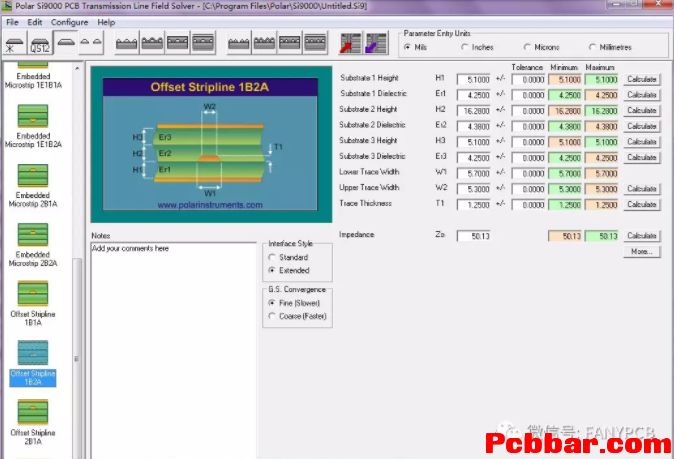

从(图二)上,可以知道各个走线层单端50R阻抗的走线宽度和参考层。其中TOP、BOTTOM层走线宽度为6mil,TOP层参考GND02层,BOTTOM参考PWR07层;ART03、ART04层走线宽度为5.7mil,ART03层参考GND02层,ART04参考GND05层;ART06层走线宽度为5.4mil, ART06参考GND05、PWR07层。具体数值我们可以从Polar SI软件中计算出来。

(1) 表层单端(TOP、BOTTOM):线宽6mil; =51.51*0.9+3.2=49.56

(2)内层单端(ART03、ART04):线宽5.7mil; =50.13

(3)内层单端(ART06):线宽5.4mil; =50.08

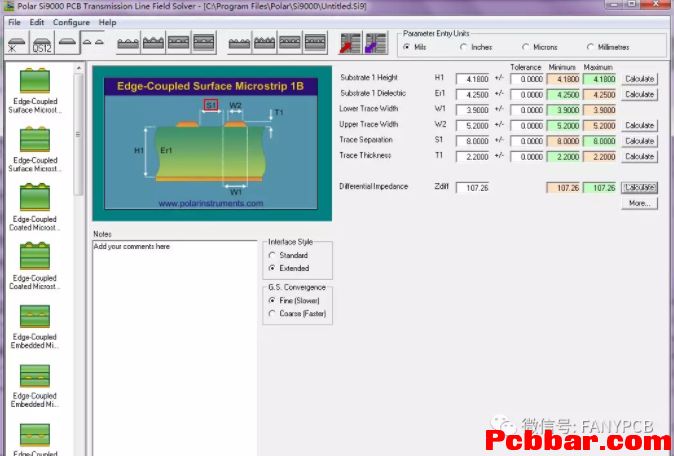

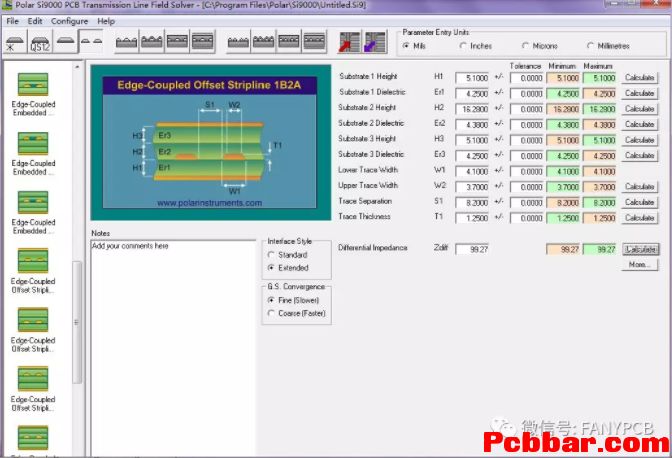

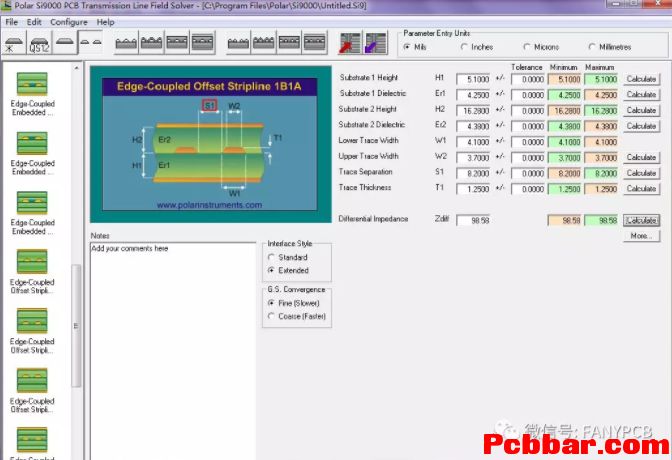

现在,接着叠层好的文件图三三、从(图三)我们可以知道各个走线层差分100R阻抗的走线宽度、线间间隙和参考层。其中TOP、BOTTOM层走线宽度为4.5mil,线与线间隙8mil,TOP层参考GND02层,BOTTOM参考PWR07层;ART03、ART04层走线宽度为4.1mil,线与线间隙8.2mil,ART03层参考GND02层,ART04参考GND05层;ART06层走线宽度为4.1mil,线与线间隙8.2mil, ART06参考GND05、PWR07层。具体数值我们可以从Polar SI软件中计算出来。(1) 表层差分(TOP、BOTTOM):线宽/线距 4.5/8mil; =107.26*0.9+3.2=99.734

(2)内层差分(ART3/ART4层): 线宽/线距 4.1/8.2mil; =99.27

(3) 内层差分(ART6层): 线宽/线距 4.1/8.2mil; =98.58

-

pcb

+关注

关注

4318文章

23045浏览量

396593 -

电路板

+关注

关注

140文章

4926浏览量

97524 -

叠层

+关注

关注

0文章

28浏览量

9831 -

可制造性设计

+关注

关注

10文章

2065浏览量

15493 -

华秋DFM

+关注

关注

20文章

3493浏览量

4422

原文标题:干货||3分钟教你看懂PCB叠层文件

文章出处:【微信号:FANYPCB,微信公众号:凡亿PCB】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

6层PCB叠层设计指南

3分钟教你看懂PCB叠层文件

3分钟教你看懂PCB叠层文件

评论