一. 概述

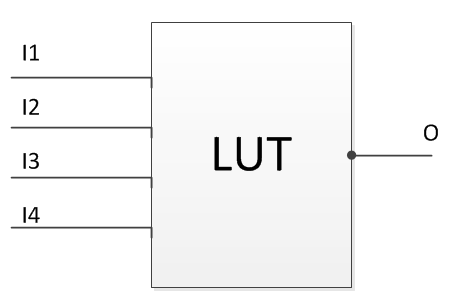

在文章《初识FPGA CLB之LUT实现逻辑函数》里面我们讲过了LUT的原理,实现逻辑函数时,相当于一个ROM将结果预存,然后把通过输入信号当作地址对预存的结果进行寻址。因此同样借助LUT加几个端口,就可以实现RAM。SLICEM里面的LUT就可以用来实现RAM资源。

二. 原理介绍

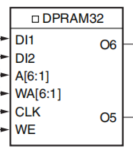

SLICEM里面的LUT跟SLICEL里面的LUT相比多了DI2,WA[6:1],CLK,WE这几个端口。做RAM用的时候,其中DI1,DI2是写数据输入端口,O5,O6同样是数据输出端口,支持一次性两bit或者单bit读写。A[6:1]为读地址,WA[6:1]为写地址,WE为写使用,CLK为时钟端口。

从这可以看出,一个LUT具有2^6=64bit的存储空间。

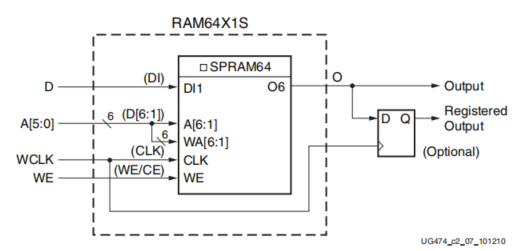

故一个LUT可以作为64x1bits的RAM(内存大小为64bit,1bit读写),地址为6位。当读写地址共用一个端口时为单端口RAM,不共用时则为双端口RAM(SLICEM里面第一个LUT的WA与A是连在一起的,故第一个LUT做不了双端口RAM)。输出数据可以经过SLICEM里面的Register资源打一拍以提高时序特性(在工具里面可以自己设置)。

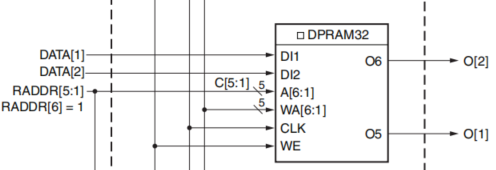

或者作为32x2bits的RAM(2bit读写),地址为5位,A[6]拉高。输出为O5,O6。

三. 扩展与提升

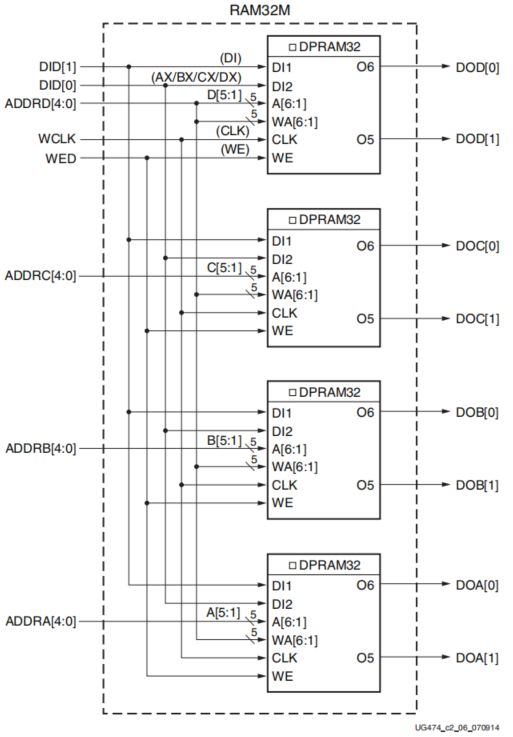

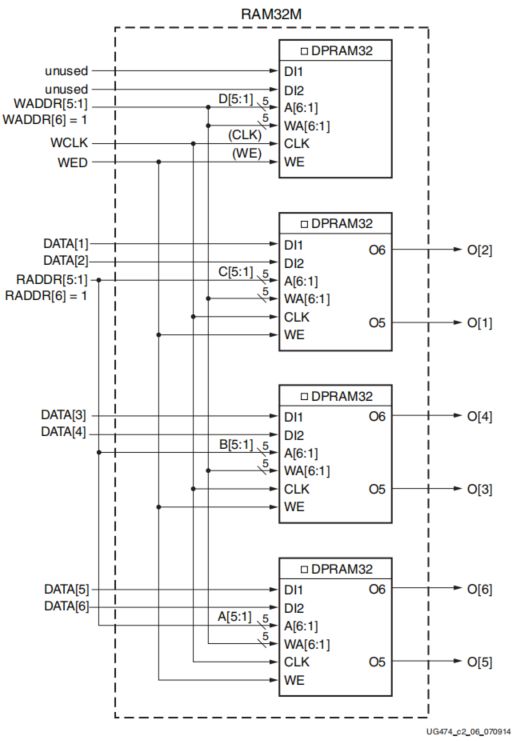

一个SLICEM里面有4个LUT,他们可以组合得到多种大小的RAM。首先就是四端口的32x2bits的RAM,支持一次性读写2bits,原理如下图。四个LUT的写数据端口DI1,DI2,写使能WE,写地址WA共用,称为写控制信号共用。读地址A分别控制。

如下图,4个LUT构成32x6bits的RAM,支持6bits读写操作。当读写共用一个地址时,就是单端口RAM,当读写不共用地址时就是双端口RAM。可以看到第一个LUT其实没用到,是因为第一个LUT的A与WA是连到一起的不能改变,所以做不了双端口。其实现原理就是3个LUT的并行2bit读写。

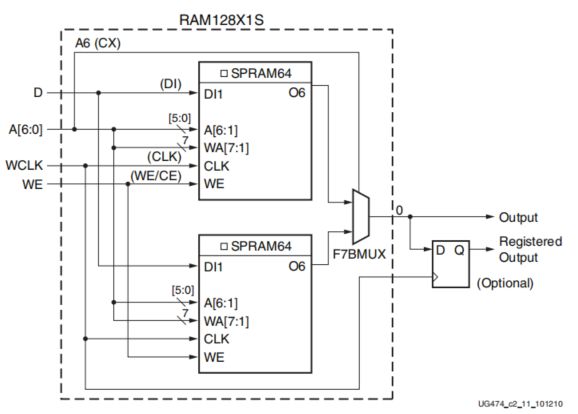

当然大家自己开动脑筋想一下也就知道了还可以组成其它什么类型的RAM,这里我们再举个例子就是借助选择器实现128x1bits的RAM。

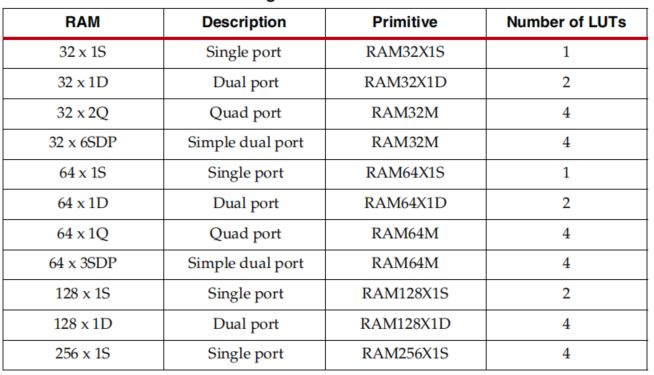

同样借助选择器在一个SLICEM里面还可以构成256x1bit的RAM,这里就不赘述,大家可以自行思考。总之在一个SLICEM里面可以实现的RAM有如下表中的几种。

多个SLICEM资源配合就可以构成更多内存大小种类的RAM。

-

RAM

+关注

关注

8文章

1378浏览量

115405 -

输出数据

+关注

关注

0文章

4浏览量

6178

原文标题:初识FPGA CLB之LUT实现RAM

文章出处:【微信号:LF-FPGA,微信公众号:小鱼FPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

FPGA重要资源CLB、Slice、LUT介绍

初识FPGA CLB之LUT实现逻辑函数

Virtex-6 FPGA上的可重配置LUT无法打包

寄存器中的RAM合成而不是LUT

SLICEM和SLICEL的输出差异怎么回事

如何读出LUT中RAM的上电值?

在FPGA设计中如何用LUT组建分布式的RAM

一文看懂ARM里的RAM和SDRAM有什么区别

FPGA内部可编程逻辑资源的结构,CLB资源介绍

Xilinx FPGA的三种片上存储资源

对于Xilinx FPGA的片上存储资源的统计介绍

FPGA的RAM存储资源详细资料说明

介绍SLICEM里的LUT如何形成RAM资源

介绍SLICEM里的LUT如何形成RAM资源

评论