关于传输线的阻抗控制,很多老司机其实都已经玩的比较溜了。下面来欣赏一下。

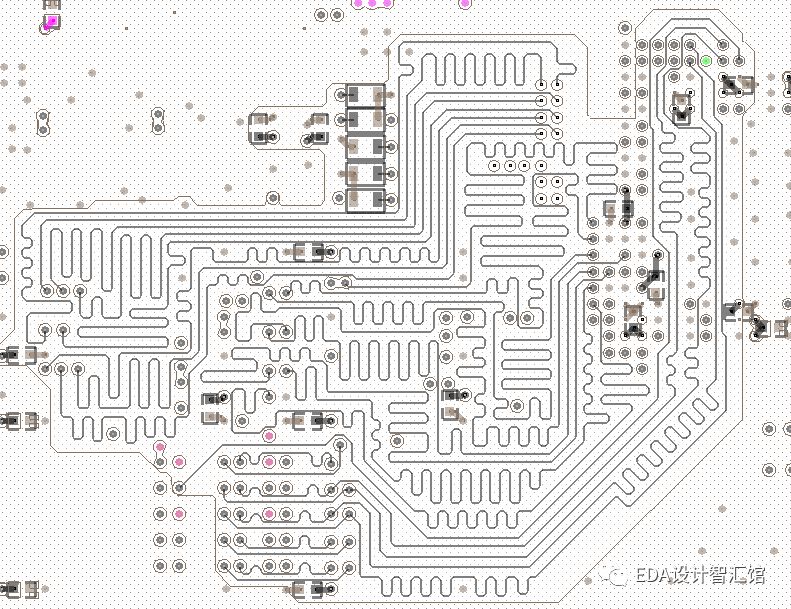

他们的阻抗设计:

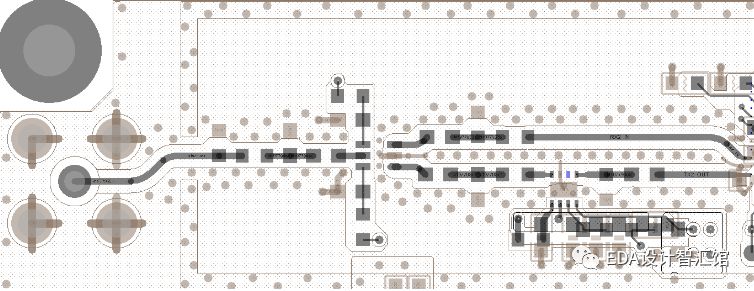

他们实测的阻抗:

高速板玩的就是阻抗,谁的阻抗玩的好,谁的高速板就玩的溜。什么传输线的阻抗,射频阻抗,过孔的阻抗,阻容器件的阻抗,高速连接器的阻抗......来,接着看。

传输线的阻抗控制

射频信号的阻抗控制

过孔的阻抗控制

阻容器件的阻抗控制

高速连接器的阻抗控制

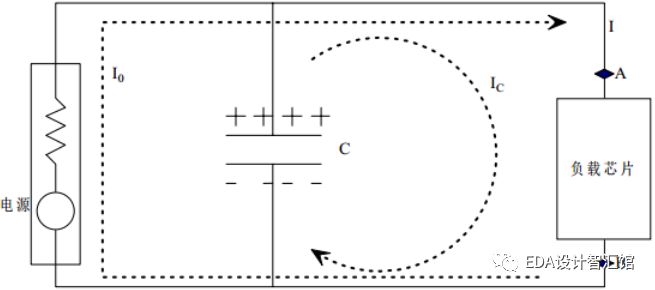

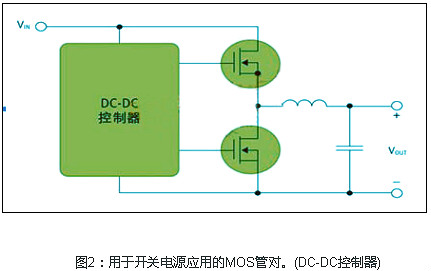

那电源的阻抗你有没有听说过?电源要不要控制阻抗?答案是肯定的。下图是一个简易的电源系统。

从AB两点向左看过去,稳压电源以及电容退耦系统一起,可以看成一个复合的电源系统。这个电源系统的特点是:不论AB两点间负载瞬态电流如何变化,都能保证AB两点间的电压保持稳定,即AB两点间电压变化很小。

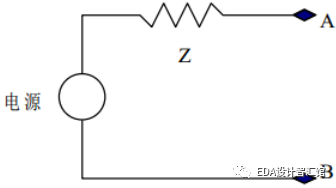

我们可以用一个等效电源模型表示上面这个复合的电源系统。

对于这个电路可写出如下等式:

我们对这个电源系统的最终设计目标是,不论AB两点间负载瞬态电流如何变化,都要保持AB两点间电压变化范围很小,这个要求等效于电源系统的阻抗Z要足够低。阻抗Z值该如何确定?这就涉及到电源的著名的目标阻抗。

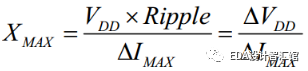

电源系统分配网络的设计要求在需要去耦的频带范围内能够满足目标阻抗,以便输出稳定的电压。在IC端放置去相电容连接在电源和地平面之间来降低PDN的阻抗。根据系统需求设计PDN的目标阻抗,其表达式为:

其中:为要进行去耦的电源电压等级,常见的有5V、3.3V、1.8V、1.26V、1.2V等。Ripple为允许的电压波动,典型值为5%。

∆I为负载芯片的最大瞬态电流变化量。该定义可解释为:能满足负载最大瞬态电流供应,且电压变化不超过最大容许波动范围的情况下,电源系统自身阻抗的最大值。超过这一阻抗值,电源波动将超过容许范围。

举例:DDR4的电压为1.2V,带4片DDR4总的最大电流为2A。那允许的电压波动=1.2V*0.05=0.06V,负载最大瞬态电流供应为2A,DDR4电源系统所允许的最大阻抗值应该为0.06/2A=30mohm。

对目标阻抗有两点需要说明:1目标阻抗是电源系统的瞬态阻抗,是对快速变化的电流表现出来的一种阻抗特性。2目标阻抗和一定宽度的频段有关。在感兴趣的整个频率范围内,电源阻抗都不能超过这个值。阻抗是电阻、电感和电容共同作用的结果,因此必然与频率有关。相同条件下的电源系统,频率越大,阻抗越大。

最终的电源系统的阻抗在不在目标阻抗之内,只有通过仿真确定。

上图很明显可以看到,在频率大于10MHz时,电源阻抗已经超过了目标阻抗,这个时候需要对应电源系统进行优化:

1.优化电源平面

2.优化电容位置

3.优化电容的安装方式

4.优化电容种类,型号和数目

5.优化层叠结构

-

电源

+关注

关注

185文章

18982浏览量

264507 -

阻抗

+关注

关注

17文章

993浏览量

49497

原文标题:走线的阻抗控制的那么好,你的电源阻抗管控的如何?

文章出处:【微信号:PCBTech,微信公众号:EDA设计智汇馆】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

如何管控你的电源阻抗

如何管控你的电源阻抗

评论