EDA(Vivado)软件可以很好的帮助我们更好的去学习FPGA相关知识,例如:

记得使用EDA软件自带的语言模板;

新建 IO Planning工程初步引脚分配;

EDA中自带的IP核你会快速用吗?

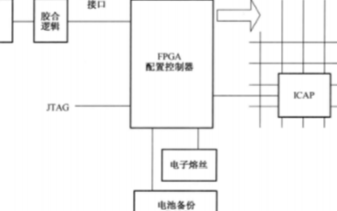

单片机是基于FLASH结构的,所以单片机上电直接从本地FLASH中运行。但SRAM 架构的FPGA是基于SRAM结构的,掉电数据就没了,所以需要借助外部电路来配置运行的数据,其实我们可以借助Vivado来学习FPGA的各种配置模式。

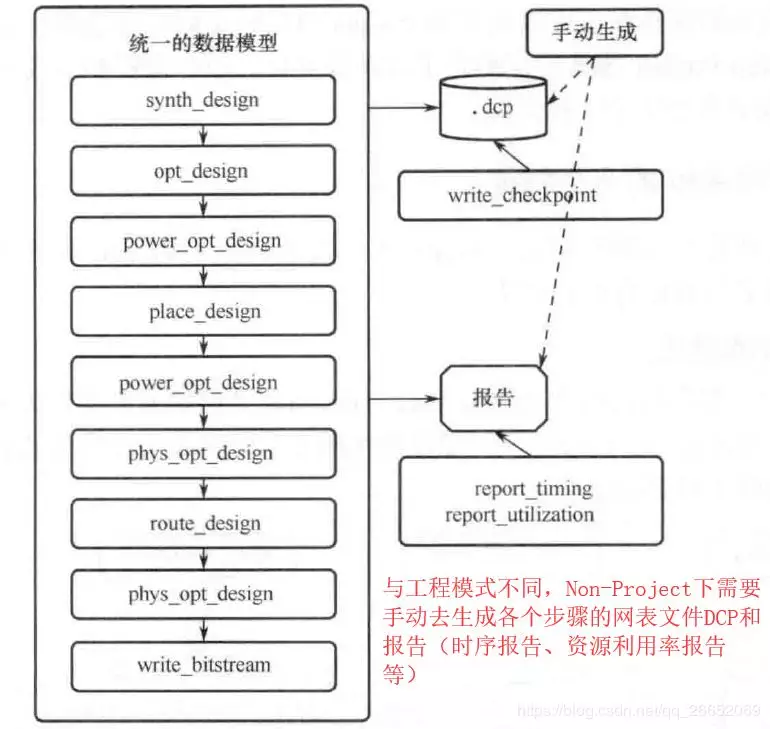

Step1,找到Vivado的设计流程框:

Step2,打开设置菜单,并选择BitSream子选项。此时,可以看到提示:Open Implemented Design后有更多的设置项可用:

Step3,当我们Open Implemented Design后,再打开这个BitSream设置菜单选项,会发现提示为Confgure additional bitstream settings,此时可以单击进入更多的设置菜单:

Step4,当我们单击进入更详细的菜单后有很多设置项,当我们打开Configuration Modes这是子设置项后,我们可以看到FPGA的各种配置模式:SPI、SelecMap、Master、Slave等,这里包括这些配置模式的参考电路和其它设置项:

Step5,打开MasterSPIx1,可以看到电路和帮助链接(7 Series Configuration User Guide),单击这个链接打开后就可以对应的帮助文档。至此,我们就可以通过这些电路和链接对应的帮助文档来学习FPGA的配置模式。

我们再打开SlaveSerial模式,在这里,可以看到电路的设计设计是可以通过外部CPLD或者MCU单片机来配置FPGA,所以有些板子你可能很奇怪只看到了FPGA+DSP而没有看到任何FLASH外设的时候,很可能就是采用DSP来配置FPGA的,FPGA的配置数据就存储在DSP的FLASH中:

这次就不具体展开FPGA的具体配置相关内容,我们可以通过Vivado让我们很直观的看到FPGA的配置模式和对应的电路设计,对我们设计开发FPGA有很大帮助。另外,FPGA多重配置可参考:

Xilinx FGPA的多重配置功能(1)

Xilinx FPGA的多重配置功能(2)

-

FPGA

+关注

关注

1663文章

22493浏览量

638944 -

单片机

+关注

关注

6078文章

45569浏览量

673312

原文标题:借助vivado来学习FPGA配置模式

文章出处:【微信号:fpga234,微信公众号:fpga234】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

借助USB来完成系统配置

如何使用Vivado Device Programmer创建和配置存储设备

FPGA JTAG的配置模式详细说明

【FPGA Vivado】基于 FPGA Vivado 的流水灯样例设计

借助Vivado来学习FPGA的各种配置模式

借助Vivado来学习FPGA的各种配置模式

评论