无论一辆汽车它是21世纪20年代初的辅助驾驶汽车,即带有用于信息娱乐系统、传动系统和自主驾驶员辅助系统(ADAS)的智能子网的汽车,还是未来3级 (Level 3)及以上的自动驾驶汽车(在车流中驾驶时只需最少的人力辅助),网络化交通系统对硬件加速的需求正在迅猛增长。几年前,由Nvidia,Mobileye和其他以CPU为中心的供应商推出的最受青睐的汽车智能模型都假设了一个集中式汽车网络,其中由带有增强DSP功能的多核RISC CPU来管理一套专用的子网络。现在,关注点正在迅速转向分布式汽车智能化,其中包含带有相关视觉系统的复杂相机,具有来自物联网世界的传感器中枢架构的传感器子网络、以及用于车载信息娱乐系统(IVI)和ADAS的附加子网络、以及传动系统/动力系统子网络,共同协作来实现自动驾驶汽车功能。

虽然Achronix预计未来的传统车辆和自动驾驶车辆最喜欢的架构都将是分布式架构,但是任何一种网络都需要比目前已经实现的架构更多的后备协处理能力。汽车网络中预期的分布式计算架构将是异构的,需要从网络控制到利用深度学习节点的并行对象识别的混合计算资源。结果,豪华辅助驾驶汽车中目前CPU的基数多达100个,而在自动驾驶汽车中可能会增加到几百个CPU。传感器中枢将需要后备图像处理来实现扭曲和拼接效果;以太网需要IP进行数据包过滤/监控,以及与传统CAN和FlexRay网络的特殊桥接。在第一代汽车架构中使用整数个CPU和GPU,将迁移到需要可编程加速的高度专业化计算节点。

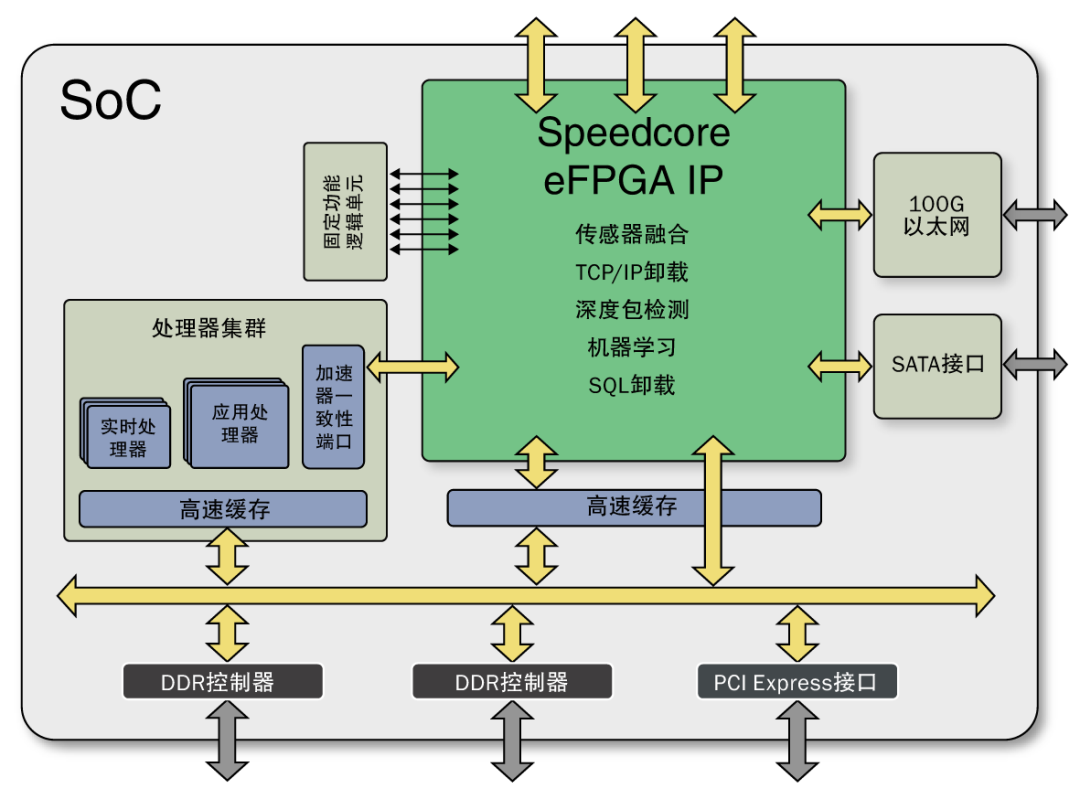

为了优化芯片面积和功率效率,在未来的汽车平台上,相比固定功能的SoC或传统的FPGA,将Speedcore™嵌入式FPGA(eFPGA)硅知识产权(IP)集成到SoC中以提供客户可配置功能,是实现快速切换协处理的一个最佳选择 。要了解更多关于处理过程的演变,请参见Achronix白皮书(WP008):SoC中的EFPGA加速 - 了解Speedcore IP设计流程。

Speedcore eFPGA IP在异构汽车数据处理中的独特作用

Speedcore eFPGA IP可以集成到ASIC或SoC中,以提供定制的可编程逻辑阵列。客户指定他们的逻辑、内存和DSP资源需求,然后Achronix配置Speedcore IP以满足他们的特定需求。Speedcore查找表(LUT)、RAM模块和DSP64模块可以像积木一样进行组合,为任何给定应用创建最佳的可编程逻辑阵列。Speedcore eFPGA IP在汽车网络集成方面提供独特的优势,无论是在现有设计中取代一个FPGA还是增强一个ASIC。

更高的性能 – 一个eFPGA通过宽阔的并行接口直接连接(无I / O缓冲器)到ASIC,提供显著更高的吞吐量,延迟仅为个位数的时钟周期。 在需要对迅速变化的交通状况进行实时响应时,延迟非常重要。

更低的功耗:

可编程I / O电路的功耗占独立FPGA总功耗的一半。一个 eFPGA直接连接到SoC,完全消除了大型可编程I / O缓冲器,从而降低了功耗。

一个eFPGA的面积可以根据最终应用的要求精确定制,并且可以调整工艺技术以实现性能和功耗的平衡。

更低的系统成本:

一个eFPGA的片芯占用面积比等效的独立FPGA小得多,这是因为可编程I / O缓冲器,未使用的DSP和存储器模块以及过度配置的LUT和寄存器都全部被移除。

借助Speedcore定制模块,可将定制功能作为附加模块添加到eFPGA逻辑阵列中,并与传统的LUT、RAM和DSP构建模块一起添加。这种高效的实施方式极大地降低了片芯尺寸面积,最大限度地降低了功耗,其总体结果就是,大大降低了系统成本。有关更多详细信息,请参阅Achronix白皮书(WP009):使用Speedcore定制模块来增强eFPGA功能。

更高的系统可靠性和良率 - 将FPGA功能集成到ASIC中,可以提高系统级信号完整性,并消除了在PCB上安装一个独立FPGA相关联的可靠性和良率损失。

以ADAS为中心的处理模型

由于多个视觉处理系统的融合被认为是驾驶辅助和自动驾驶车辆的核心,所以先进驾驶员辅助系统(ADAS)在未来的汽车架构中保持了核心地位,即使被认为是管理者中的管理者的多核视觉处理器,也已经部分被取代了。涉及DSP和整数密集型任务两者的图像实时处理,最初被认为是从静态相机或视频图像中提取信息以确定对象类型、位置和速度的问题。随着设计人员为自动驾驶车辆做准备,ADAS处理器的角色已经扩展到包括视觉、红外、超声波、激光雷达(LIDAR)和雷达图像的融合。在传统的SoC和协处理器套件中,图像预处理与CPU分开执行,并且必须通过一个或多个高速总线与CPU连接。即使ADAS架构的总线延迟得到改善,当协处理器在单独的芯片中实现时,也会付出延迟的代价。因此,将eFPGA IP与统一ADAS架构中的CPU相结合,以确保在快速变化的交通状况中有视觉、红外或雷达警报的快速响应,这是可以验证的最有效的方式。

将多个传感器源与一个ADAS内核集成在一起,提供了Speedcore IP与一个CPU并行嵌入的一种理想应用场景。 Speedcore IP支持客户将一个定制的可编程逻辑阵列嵌入到具有专用计算资源的标准化ASIC平台中(请参见下图,并请参阅第4页)。在实践中,这种集成化可以将从图像源汇总的数据写入CPU的缓存,而不是写入独立的SDRAM。 减少CPU的中断意味着对移动中汽车视野里的物体有更多的实时响应。

视觉处理器(通常来自相机输入的2D图像,尽管已包括越来越多的3D图像)可以依靠多年来在边缘提取、格式转换、色彩平衡和分辨率变化方面积累的图形处理器研究。包括Ceva和Synopsys在内的一些处理器IP供应商,也在对象分类和识别中提升了卷积神经网络的价值。以Nvidia为代表的,在这两个领域都有经验的CPU供应商,已经试图在传统的CPU / GPU任务与特定的神经网络模式识别引擎之间取得平衡。对于汽车中的神经网络子架构,正从需要高精度浮点DSP的早期成熟架构迁移到能够使用低精度DSP内核的自我培训推理引擎,Speedcore DSP64模块为新的深度学习架构提供了大量的开销。 对ADAS和视觉处理演变的一个共同认识是,实时汽车的态势感知永远不会有一个最佳的集中式ADAS处理器或SoC。总是会有意想不到的协同处理和加速任务被添加到ADAS中心内核中。

任何ADAS处理器固有的两项附加功能是传感器融合/中枢集成和网络转换。前者涉及将来自各种传感器的信息进行组合和关联:包括CMOS图像、红外、激光雷达和新兴的小型化雷达等传感器。网络转换是指以太网的主干网络与CSI-2、FlexRay、CAN甚至更早的网络协议的接口。虽然未来的一个ADAS SoC确实可以集成一个传感器中枢或一个以太网MAC,但总是会有一些新兴的功能,由CPU外部的外围逻辑极好地提供。由于传感器被聚合并且网络在输入到CPU之前在芯片内互连,所以通过减少暴露的接口来保持安全性是一个解决方案,同时通过片上集成来提高可靠性,对于许多这样的任务而言将被证明是最佳的方案。

图1:Speedcore阵列(左上)链接到CPU子系统及内存集群

-

FPGA

+关注

关注

1629文章

21748浏览量

603997 -

智能化

+关注

关注

15文章

4897浏览量

55463

原文标题:Speedcore eFPGA 在汽车智能化中的应用

文章出处:【微信号:FPGAer_Club,微信公众号:FPGAer俱乐部】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

上位机实时数据处理技术 上位机在智能制造中的应用

FPGA 实时信号处理应用 FPGA在图像处理中的优势

Achronix Speedcore eFPGA的特性和功能

FPGA在数据处理中的应用实例

Primemas选择Achronix eFPGA技术用于Chiplet平台

浅谈国产异构双核RISC-V+FPGA处理器AG32VF407的优势和应用场景

Achronix FPGA增加对Bluespec提供的基于Linux的RISC-V软处理器的支持,以实现可扩展数据处理

工程监测振弦采集仪在振动监测中的应用与数据处理技术

Speedcore eFPGA IP在异构汽车数据处理中的独特作用

Speedcore eFPGA IP在异构汽车数据处理中的独特作用

评论