近日,基于RISC-V指令集的软核CPU在SWORD4.0上顺利移植,给予用户对SWORD4.0的新体验,用户甚至可以通过Arduino IDE开发RISC-V应用。

在SWORD4.0上移植的是基于RISC-V指令集的F32C开源CPU。CPU通过配置既可以支持RISC-V指令集也可以支持MIPS指令集。

图1F32C github

用户通过对Arduino IDE简单升级,可以使Arduino IDE支持SWORD4.0的RISC-V编译工作。图形化编程环境和大量Arduino范例都有利于用户进行应用开发。

图2升级后的Arduino IDE可以进行RISC-V编译

图3用RISC-V CPU控制LED亮度

图4用RISC-V CPU控制串口输入输出

图5用RISC-V CPU控制7段数码管

RISC-V完全开源、极度精简,非常适合物联网和边缘计算等应用。RISC-V作为SWORD生态系统的一部分,为计算机系统能力培养提供着澎湃动力。

-

cpu

+关注

关注

68文章

10901浏览量

212927 -

生态系统

+关注

关注

0文章

703浏览量

20779 -

RISC-V

+关注

关注

45文章

2322浏览量

46548

原文标题:RISC-V助力SWORD生态系统演进

文章出处:【微信号:gh_94c30763133f,微信公众号:FPGA那点事儿】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

浅谈RISC-V指令集架构的来龙去脉

【RISC-V开放架构设计之道|阅读体验】RISC-V基础整数指令集

RISC-V基础整数指令集

RISC-V指令集的特点总结

RISC-V和arm指令集的对比分析

RISC-V指令集概述

印度确立RISC-V为国家指令集 中国CPU指令集还在孤芳自赏

RISC-V指令集的起源与发展历史

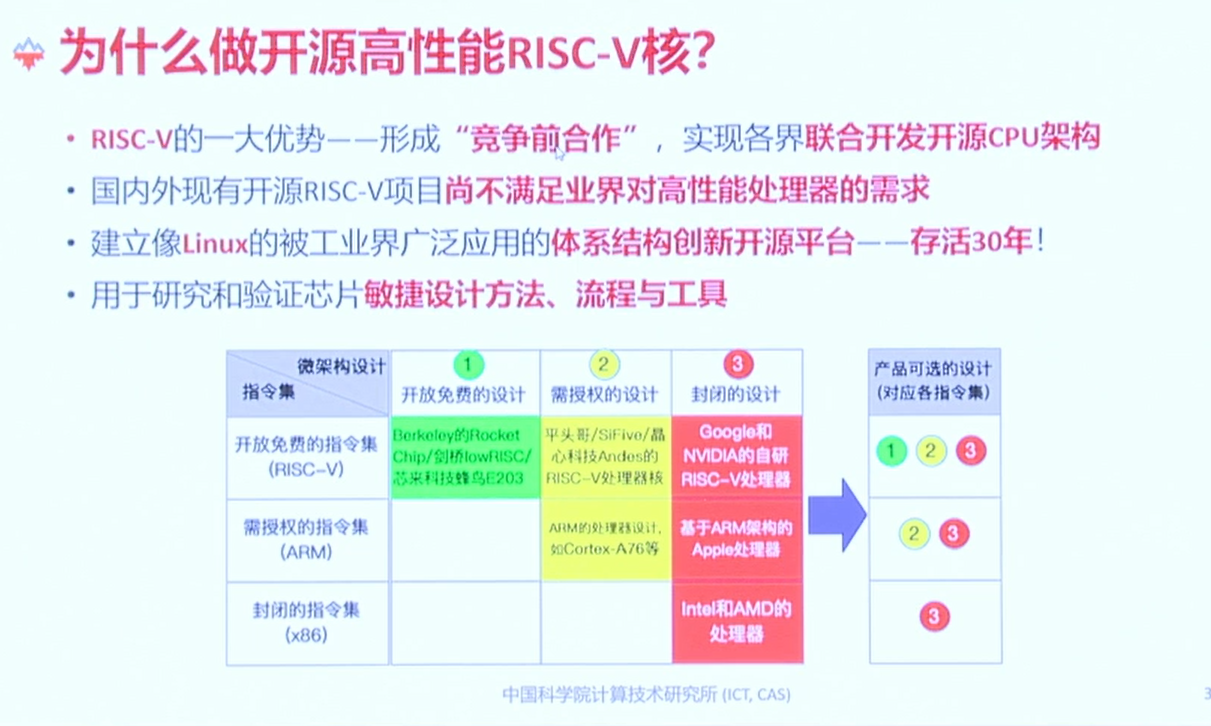

为什么做开源高性能RISC-v核,香山开源高性能RISC-V处理器开发流程

什么是RISC-V?RISC-V指令集的优势

基于RISC-V指令集的软核CPU在SWORD4.0上顺利移植

基于RISC-V指令集的软核CPU在SWORD4.0上顺利移植

评论