深度学习有一个DRAM问题。设计用来实时处理复杂任务(比如,在汽车的备份摄像头视频流中分辨猫和孩子)的系统,不断地将构成神经网络内容的数据从存储器传送到处理器。

根据初创公司Flex Logix的说法,问题并不是缺乏存储这些数据的空间,而是处理器和存储器之间缺乏带宽。为了将数百千兆比特的数据提供给处理器,有些系统需要4个甚至8个DRAM芯片,这既使占用的空间增加了不少,又消耗了大量的电能。Flex Logix表示,它为可重构芯片开发的互连技术和tile-based架构将使AI系统只需要1个DRAM芯片的带宽,且功耗仅为十分之一。

图片来源:Flex Logix

NMAX512tile的架构。

位于加州山景城的Flex Logix公司已经开始将一种新的嵌入式现场可编程门阵列(eFPGA)架构商业化。但经过一番探索后,其创始人之一Cheng C. Wang意识到,这项技术可以加快神经网络的速度。

神经网络由连接和表示连接强度的“权重”组成。另一位创始人Geoff Tate解释说,一个好的AI芯片需要两样东西。一种是一些做关键“推断”计算(即乘法和累加)的电路。“但更困难的是,你必须非常擅长引入所有这些权重,以便其乘法器总能得到它们需要的数据,从而进行所需的数学运算。Wang意识到我们在FPGA的互连方面所拥有的技术,他可以对它做适应性改造,来创建一种非常擅长快速高效地加载权重、高性能和低功耗的架构。”

需要快速连续地将数百万个权重加载到网络中,这就是每秒要做数万亿次到数十万亿次运算的AI系统为什么需要那么多DRAM芯片的原因。DRAM芯片上的每个引脚每秒最多可以传输4Gb数据,因此要达到所需的每秒数百Gb的数据传输速度,就需要多个芯片。

在为FPGA开发最初的技术时,Wang注意到,这些芯片有约80%的面积互连,因此他寻求一种能够缩小互连面积并考虑到更多逻辑的架构。他和他在加州大学洛杉矶分校的同事对一种称为folded-Beneš网络的电信架构做了适应性改造来完成这项工作。这使得FPGA架构看起来像一堆逻辑和SRAM的瓦片(tile)。

图片来源:Flex Logix

Flex Logix公司表示,在芯片中构建分布式SRAM可加快计算速度并降低功耗。

Tate说,在这种专用互连方案中使用分布式SRAM最终会对深度学习的DRAM带宽问题产生重大影响。“我们正在用芯片上的SRAM取代DRAM带宽。”

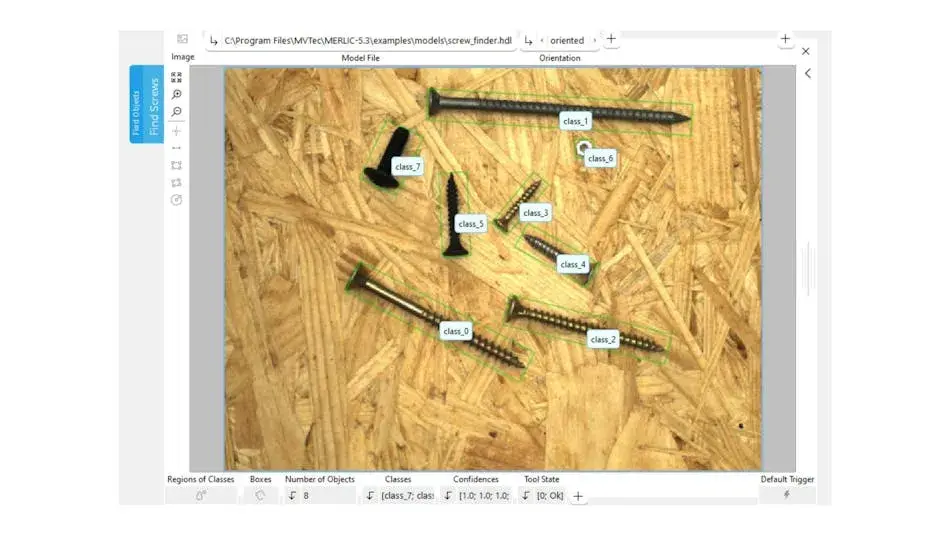

图片来源:Flex Logix

若干NMAXtile可以置于一个芯片上并连在一起,以扩大计算能力。

用于Flex Logix的AI产品的tile称为NMAX,采用了台积电的16纳米技术,面积不到2平方毫米。每个tile都由一组核心组成,这些核心这些核心负责关键的乘法和累加计算、控制数据的处理和流动的可编程逻辑以及SRAM。这涉及三种不同类型的互连技术。一种tile上的所有零件连接在一起。另一种将tile与位于tile之间的附加SRAM及外部的DRAM相连接。第三种将相邻的tile连接在一起。

在深度学习领域,很难进行真正的横向比较。但Flex Logix的分析显示,将使用1个DRAM芯片的模拟的6×6tile的NMAX512阵列与使用8个DRAM的Nvidia Tesla T4进行比较,结果是新架构每秒能识别4,600张图像,而Nvidia每秒识别3,920张图像。在一项名为YOLOv3的实时视频处理测试中,同样大小的NMAX阵列可达到每秒22万亿次运算,而使用的DRAM带宽是其他系统的十分之一。

Tate表示,首批NMAX芯片的设计将于2019年下半年送至代工厂以便进行制造。

Flex Logix将波音公司视作其高吞吐量嵌入式FPGA产品的客户之一。但Tate承认,与神经网络相比,嵌入式FPGA是个很难卖的产品。“嵌入式FPGA是一项很好的业务,但是推理可能很快就会超越它。”Tate说。

-

DRAM

+关注

关注

41文章

2403浏览量

189704 -

神经网络

+关注

关注

42文章

4844浏览量

108292 -

深度学习

+关注

关注

73文章

5613浏览量

124706

原文标题:Flex Logix公司称它解决了深度学习的DRAM问题

文章出处:【微信号:IEEE_China,微信公众号:IEEE电气电子工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

探索VEEDER - ROOT FLEX系列面板仪表的魅力

探索VEEDER - ROOT的FLEX®/FLEX MINI®面板仪表

深度学习为什么还是无法处理边缘场景?

EZ-USB® NX2LP-Flex™:灵活的USB NAND闪存控制器深度剖析

Debian flex-installer 无法下载引导映像怎么解决?

人工智能与机器学习在这些行业的深度应用

创新的高带宽DRAM解决方案

穿孔机顶头检测仪 机器视觉深度学习

Flex Power Modules将产品制造扩展至欧洲

如何深度学习机器视觉的应用场景

PSRAM融合SRAM与DRAM优势的存储解决方案

如何在机器视觉中部署深度学习神经网络

深度学习对工业物联网有哪些帮助

自动驾驶中Transformer大模型会取代深度学习吗?

Flex Logix公司称它解决了深度学习的DRAM问题

Flex Logix公司称它解决了深度学习的DRAM问题

评论