11月4日,天津市滨海新区信息技术创新中心对外发布了我国首款自主研发的RapidIO二代交换芯片——NRS1800。该芯片在数据计算、数据采集、数据存储、对外通信领域具有领先优势,可广泛应用于图像分析、医疗成像、数据中心等领域,填补了我国在交换芯片领域空白。

“未来交换芯片的市场规模可达到千亿级。”据创新中心相关技术负责人介绍,RapidIO二代交换芯片在信息基础设施建设,如无线通信、数据中心、云计算、高性能计算等领域都已得到大规模应用。创新中心技术人员经过历时近4年的攻关研发,实现了NRS1800的量产流片和批量供货。目前,该芯片在全国十余家单位得到应用。

天津市滨海新区信息技术创新中心是软件定义互连技术及产业发展联盟牵头单位,未来创新中心芯片研发团队将继续围绕软件定义互连技术方向开展RapidIO第三代交换芯片、软件定义互连芯片等交换芯片的研制,助力国家网络强国发展战略建设。

据了解,RapidIO技术主要面向高性能嵌入式系统的互连通信,被广泛应用于高性能嵌入式系统芯片间、板卡间乃至设备间的互连,是一种高性能、低引脚数的互连体系结构,具有高带宽、低时延、高效率、高可靠性等优点。

RapidIO: 高性能嵌入式互连技术

RapidIO互连架构是一个开放的标准,满足了嵌入式基础设施在应用方面的广泛需要。可行的应用包括连接多处理器、存储器、网络设备上的存储器映射I/O器件、存储子系统和通用计算平台。

RapidIO互连定义包括两类技术:面向高性能微处理器及系统互连的并行接口;面向串行背板、DSP和相关串行控制平面应用的串行接口。串行和并行RapidIO具有相同的编程模型、事务处理和寻址机制。

RapidIO支持的编程模型包括基本存储器映射I/O事务、基于端口的消息传递和基于硬件一致性的全局共享分布式存储器。RapidIO也提供各种错误检测机制,还提供定义良好的硬件和基于软件的架构以报告并纠正传输错误。

RapidIO互连被定义为分层结构,在保证后向兼容性的同时提供了可扩展性和未来增强的可能。

RapidIO协议分层结构

逻辑层定义了操作协议; 传输层定义了包交换、路由和寻址机制;物理层定义了电气特性、链路控制和纠错重传等。

象以太网一样,RapidIO也是基于包交换的互连技术。如图3所示,RapidIO包由包头、可选的载荷数据和16bits CRC校验组成。包头的长度因为包类型不同可能是十几到二十几个字节。每包的载荷数据长度不超过256字节,这有利于减少传输时延,简化硬件实现。

RapidIO技术主要面向高性能嵌入式系统的互连通信,它采用高性能LVDS技术,可以在4对差分线上实现10Gbps的有效传输速率,而且具有万兆以太网、PCI express更高的传输效率。由于RapidIO在路由、交换、容错纠错、使用方便性上有较完善的考虑,可以实现基于硬件的高性能可靠数据传输,所以必将在嵌入式系统、3G和3G之后的Beyond3G、4G移动通信基站、高性能数字信号处理系统等中得到广泛应用。

大多数电子系统实现三个基本功能:处理数据、来回移动数据和存储数据,即在处理和传输数据时,也在沿途不同的地方存储这些数据。开发RapidIO技术正是为了在嵌入式系统内提供以交换互连而非总线为基础的传输数据的标准方法,从而能够替代很多现有总线技术或基于交换的技术如PCI、VME、Utopia、Infiniband、Ethernet(在系统内使用)或者SPI4。

-

存储

+关注

关注

13文章

4292浏览量

85782 -

交换芯片

+关注

关注

0文章

81浏览量

11009

原文标题:我国首款自主研发RapidIO二代交换芯片正式发布

文章出处:【微信号:iawbs2016,微信公众号:宽禁带半导体技术创新联盟】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

苹果计划2025年起采用自研蓝牙Wi-Fi芯片

AMD推出第二代Versal Premium系列

比亚迪最快于11月实现自研算法量产,推进智驾芯片自研进程

一加正式发布第二代东方屏,获全球首个DisplayMate A++认证

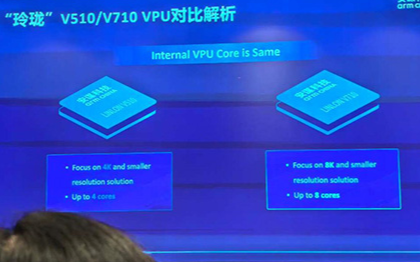

本土自研再上新!安谋科技发布首款“玲珑”DPU和新一代VPU

srio交换芯片是什么?srio交换芯片的原理和作用

airpods一代和二代区别充电仓

中科驭数自研第二代DPU芯片K2获得行业认可

智绘微电子第二代自研桌面级国产GPU芯片IDM929成功点亮

特斯拉二代4680电芯拆解分析

我国自研RapidIO二代交换芯片正式发布

我国自研RapidIO二代交换芯片正式发布

评论