安装Design Utilities

使用report_failpast之前,要先确保Design Utilities已经安装。安装方法是点击Tools->Xilinx Tcl Store,如下图所示。

02

report_failpast生成报告

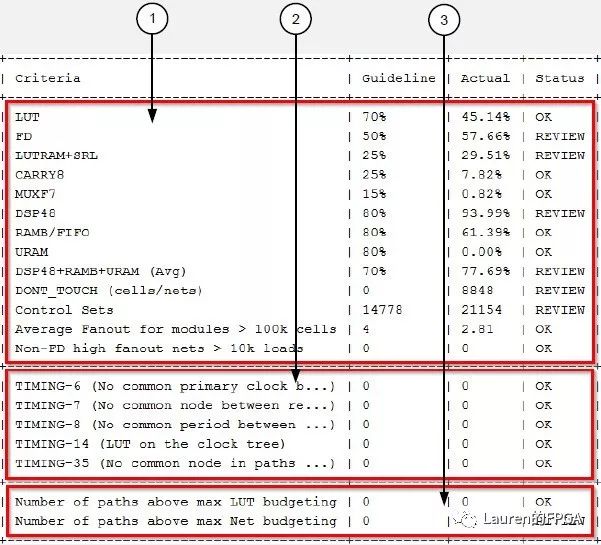

report_failpast生成的报告分为三部分:设计特征、时钟检查和关键路径分析,如下图所示。其中在设计特征部分,该报告会给出资源利用率的建议值,一旦超过这个建议值,Status列内会呈现REVIEW标记。如图中的FD(D触发器),实际利用率为57.66%,超过建议值50%。同时该部分还会给出控制集分析(Control Set),可帮助判断是否需要降低控制集。此外,对于不是由FD驱动的扇出大于10K的net,这部分也会有所显示。

图片来源:page 10, ug1292

03

report_failpast使用方法

report_failpast除了基本的使用方法(不添加任何选项)之外,还提供了其他的选项。例如,-pblock选项可用于分析Pblock对应的约束是否合理。该选项可在布局之前使用(要求已经提供了Pblock具体位置约束),也可在布局之后使用。显然,在布局之前使用是非常有意义的,因为可以据此判定Pblock的约束是否合理。同时,针对SSI芯片,该命令还提供了-slr和-by_slr选项,这两个选项需要在布局之后使用。此外,对于报告中Status为REVIEW的条目可通过选项-detailed_report生成相应的更为详细的报告,具体使用方法如下所示。例如,DONT_TOUCH为REVIEW状态,则该命令可生成impl.DONT_TOUCH.rpt报告,可显示使用了DONT_TOUCH属性的cell。

xilinx::designutils::report_failfast

-detailed_report impl -file failfast.rpt

report_failfast的另一特征在于既可以应用于整个设计,也可以针对某个指定的模块进行分析。例如,对于设计中的关键模块采用此命令分析,可预先发现潜在的问题,从而加速时序收敛。

-

芯片

+关注

关注

456文章

51157浏览量

426807 -

触发器

+关注

关注

14文章

2003浏览量

61314

原文标题:深度解析ug1292(10)

文章出处:【微信号:Lauren_FPGA,微信公众号:FPGA技术驿站】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

FPGA User Guide之report_cdc

如何通过report_utiliztion获得切片比率?

ETSI TECHNICAL REPORT ETR 289

Reference Design Report for a

Reference Design Report for a

Reference Design Report for a

Engineering Prototype Report f

WEBENCH ® Design Report_1054927/8_TPS61256YFFR

如何使用report_cdc命令分析、调试和修复CDC问题

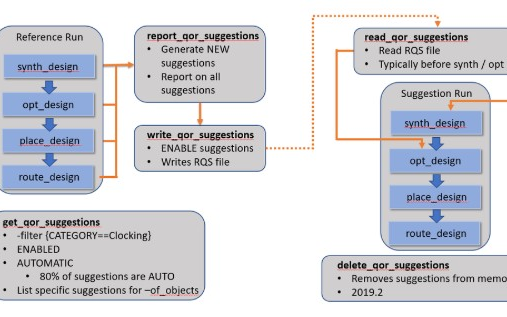

Report QoR Suggestions助力解决Vivado设计问题

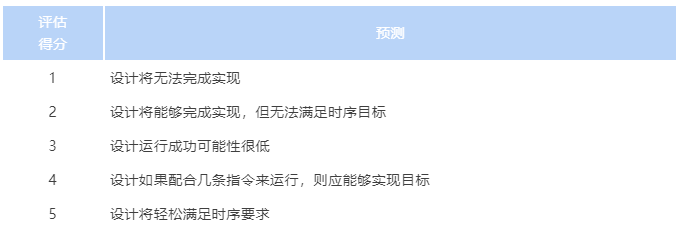

FPGA设计:关于Report QoR Assessment 命令的使用

AD9217 and Intel Stratix 10 Interoperability report and Reference Design

如何使用report_failfast

如何使用report_failfast

评论