声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

视频

+关注

关注

6文章

1962浏览量

73265 -

赛灵思

+关注

关注

32文章

1794浏览量

131665 -

调试

+关注

关注

7文章

591浏览量

34147

发布评论请先 登录

相关推荐

【米尔-Xilinx XC7A100T FPGA开发板试用】 UART测试

例程遇到些问题,原代码涉及时钟IP没法跑通,修改了之后可以跑通了。

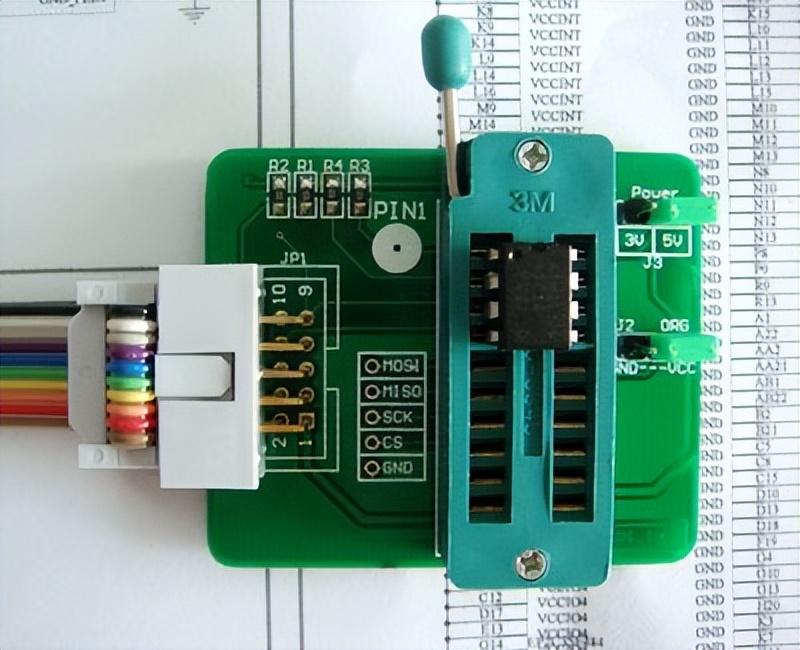

下图是修改后的schematic

烧写结果:

微软的串口调试助手验证:

本次串口功能测试 ,串口通信功能完全正常,通信稳定可靠。

发表于 01-12 10:10

ZYNQ基础---AXI DMA使用

Xilinx官方也提供有一些DMA的IP,通过调用API函数能够更加灵活地使用DMA。 1. AXI DMA的基本接口 axi dma IP的基本结构如下,主要分为三个部分,分别是控制axi

如何进行电子连接器的测试与验证

电子连接器的测试与验证是确保其性能和质量的关键步骤。以下是对电子连接器进行测试与验证的方法: 一、测试与验证的目的 电子连接器的测试与验证旨

调试Xilinx Zynq + ADS58C48,ADC使用的是LVDS模式,ADC不能正常工作怎么解决?

我正在调试Xilinx Zynq + ADS58C48,ADC使用的是LVDS模式,ADC不能正常工作。有以下几点问题:

1)通过Xilinx FPGA差分原语输给ADC一个10MHz的差分时

发表于 12-10 07:34

AMBA AXI4接口协议概述

AMBA AXI4(高级可扩展接口 4)是 ARM 推出的第四代 AMBA 接口规范。AMD Vivado Design Suite 2014 和 ISE Design Suite 14 凭借半导体产业首个符合 AXI4 标准的即插即用型 IP 进一步扩展了 AMD 平台

解决验证“最后一公里”的挑战:芯神觉Claryti如何助力提升调试效率

过程中必不可少的一环,它帮助工程师找到问题的根源并进行优化。随着设计复杂性的提升,调试作为验证的“最后一公里”正面临越来越多的挑战。如何有效提升调试效率,已成为行

解锁SoC “调试”挑战,开启高效原型验证之路

引言由于芯片设计复杂度的提升、集成规模的扩大,以及产品上市时间要求的缩短,使得设计验证变得更加困难。特别是在多FPGA环境中,设计调试和验证的复杂性进一步增加,传统的调试手段难以满足对

快速部署原型验证:从子卡到调试的全方位优化

引言原型验证是一种在FPGA平台上验证芯片设计的过程,通过在FPGA上实现芯片的设计原型,使得开发人员可以在硬件完成之前提前开始软件开发和系统验证。然而,如何快速确保在原型验证平台上开

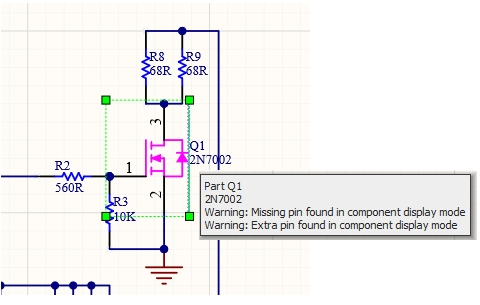

对元件显示模式下发现的验证错误进行故障排除

对原理图进行电气规则检查时的验证错误进行故障排除,例如,“Missing pin found in component display mode”或“Extra pin found in component display mo

Xilinx NVMe AXI4主机控制器,AXI4接口高性能版本介绍

NVMe AXI4 Host Controller IP可以连接高速存储PCIe SSD,无需CPU,自动加速处理所有的NVMe协议命令,具备独立的数据写入和读取AXI4接口,不但适用高性能、顺序

深度学习的模型优化与调试方法

深度学习模型在训练过程中,往往会遇到各种问题和挑战,如过拟合、欠拟合、梯度消失或爆炸等。因此,对深度学习模型进行优化与调试是确保其性能优越的关键步骤。本文将从数据预处理、模型设计、超参数调整、正则化、模型集成以及调试与

有关PL端利用AXI总线控制PS端DDR进行读写(从机wready信号一直不拉高)

,DDR就不会拉高wready信号,验证如图所示,必须你首先给wvalid信号,wready信号才会拉高

情形二:如果设置为AXI3,如图所示

经过验证发现,最后DDR会一开始就拉高wready信号

发表于 05-31 12:04

SoC设计中总线协议AXI4与AXI3的主要区别详解

AXI4和AXI3是高级扩展接口(Advanced eXtensible Interface)的两个不同版本,它们都是用于SoC(System on Chip)设计中的总线协议,用于处理器和其它外设之间的高速数据传输。

FPGA通过AXI总线读写DDR3实现方式

AXI总线由一些核心组成,包括AXI主处理器接口(AXI4)、AXI处理器到协处理器接口(AXI4-Lite)、

发表于 04-18 11:41

•1430次阅读

如何使用Xilinx AXI进行验证和调试

如何使用Xilinx AXI进行验证和调试

评论