本视频将指您介绍如何使用Vivado设计套件中的交互式“IO Pin Planning”和“Device Exploration”功能。具体来说,IO规划包括:在设计中创建,配置,分配和管理IO端口以及时钟逻辑 对象。该视频教程描述了在设计流程的不同阶段如何执行IO规划的步骤。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

IO

+关注

关注

0文章

433浏览量

39035 -

赛灵思

+关注

关注

32文章

1794浏览量

131111 -

逻辑

+关注

关注

2文章

831浏览量

29422

发布评论请先 登录

相关推荐

使用Vivado通过AXI Quad SPI实现XIP功能

本博客提供了基于2023.2 Vivado的参考工程,展示如何使用Microblaze 地执行(XIP)程序,并提供一个简单的bootloader。

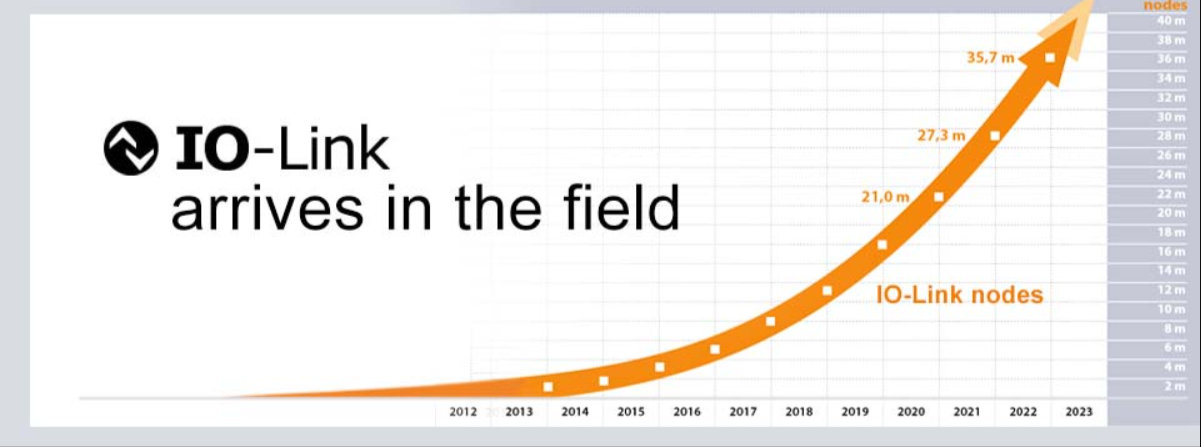

本地IO与远程IO:揭秘工业自动化中的两大关键角色

在工业自动化领域,IO(Input/Output,输入/输出)模块扮演着至关重要的角色。它们作为连接控制系统与现场设备的桥梁,负责数据的采集与指令的执行。然而,随着技术的不断进步,IO

远程IO与分布式IO的区别

在工业自动化和控制系统设计中,远程IO(Input/Output)和分布式IO是两个重要的概念。它们各自具有独特的特点和优势,适用于不同的应用场景。本文将详细探讨远程

在不重新安装Vivado的情况下,是否能够安装线缆驱动器?

如果 Xilinx USB/Digilent 线缆驱动器在安装 Vivado 设计套件时还没有安装,或者 Xilinx USB/Digilent 线缆驱动器被禁用,在不全面重新安装

Vivado编译常见错误与关键警告梳理与解析

Xilinx Vivado开发环境编译HDL时,对时钟信号设置了编译规则,如果时钟由于硬件设计原因分配到了普通IO上,而非_SRCC或者_MRCC专用时钟管脚上时,编译器就会提示错误。

verilog中for循环是串行执行还是并行执行

在Verilog中,for循环是并行执行的。Verilog是一种硬件描述语言,用于描述和设计数字电路和系统。在硬件系统中,各个电路模块是同时

EtherCAT IO的接线方法和流程是怎样的?

(例如传感器和执行器)的接线和配置过程。 一、EtherCAT IO的基本概念 在详细讨论具体的接线方法和流程之前,我们首先需要了解EtherCAT IO的基本概念。 1.

如何禁止vivado自动生成 bufg

在Vivado中禁止自动生成BUFG(Buffered Clock Gate)可以通过以下步骤实现。 首先,让我们简要了解一下什么是BUFG。BUFG是一个时钟缓冲器,用于缓冲输入时钟信号,使其更稳

GNSS技术在城市规划中的革新:精准定位引领智慧城市发展

随着城市化的快速推进,城市规划愈发关键,而全球导航卫星系统(GNSS)技术的广泛应用正为城市规划带来一场前所未有的变革。本文将深入探讨GNSS模块在城市规划

信号驱动IO与异步IO的区别

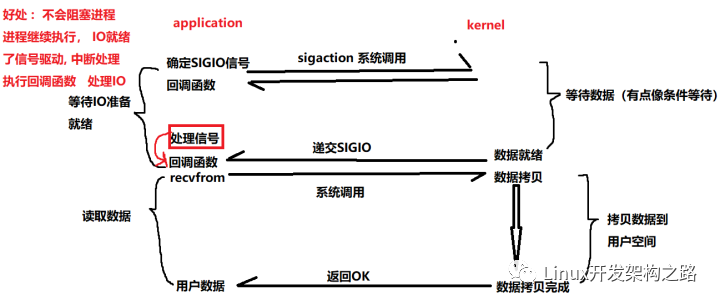

, 是开始处理IO, 这个时候还是存在阻塞的,将数据从内核态拷贝进入到用户态的过程至少是阻塞住的 (应用程序将数据从内核态拷贝到用户态的过程是阻塞等待的, 和异步IO的区别) (此处是区分信号驱动IO和异步

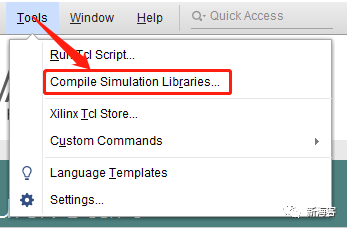

Vivado2018版本中Modelsim的配置

Vivado自带的仿真工具在一些基本功能的仿真测试时是可以满足的,但如果你的工程较为庞大,那么自带的仿真工具将有些勉强,除了在数据输出方面的卡顿,在仿真速度上也可能无法接受,这里可以借助第三方仿真工具进行工程仿真测试,

在Vivado设计套件中如何执行IO的规划

在Vivado设计套件中如何执行IO的规划

评论