这个Xilinx Quick Take Video我们将讨论Constraint Explosion。 在本次会议中,我们将研究导致时序约束爆炸的原因,然后是如何调试和修复异常约束问题。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

赛灵思

+关注

关注

32文章

1794浏览量

131334 -

调试

+关注

关注

7文章

582浏览量

33973

发布评论请先 登录

相关推荐

时序约束一主时钟与生成时钟

的输出,对于Ultrascale和Ultrascale+系列的器件,定时器会自动地接入到GT的输出。 1.2 约束设置格式 主时钟约束使用命令create_clock进行创建,进入Timing

常用时序约束使用说明-v1

为了防止约束失败,我们在Tcl输入框中验证,没有告警或者错误说明约束的写法是正确的set_max_delay 5.00 -from [get_cells key2_detect_inst/state

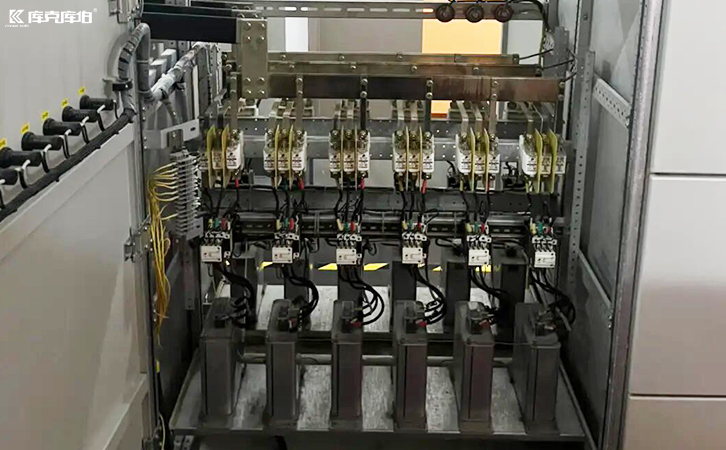

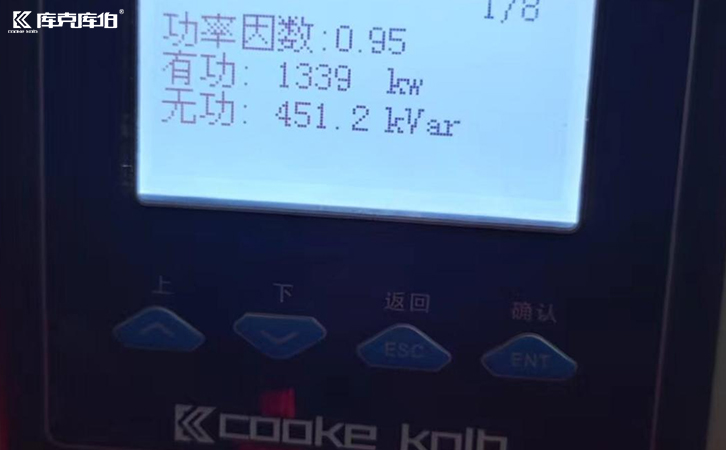

电容补偿柜的保险爆炸的原因

了生产的安全性和稳定性。本文将详细探讨电容补偿柜保险爆炸的原因,并提出有效的预防措施,以期为相关领域的同仁提供参考。 电容补偿柜的保险丝爆炸可能由以下几个原因导致: 过载 :当电容器组

电容柜接电瞬间爆炸的原因分析

爆炸的原因分析 1、电容器选择不当 电容柜使用的电容器规格必须与电力系统的电压及电流等级匹配。如果选择了不适当的电容器,接电时可能产生过大的电流,导致电容器内部元件过热,引发电气故障和爆炸

电源时序器跳闸的原因和解决方法

电源时序器跳闸是一个常见的电气问题,它可能由多种因素引起,包括电源电压不稳定、电路短路、过载电流以及时序器本身的故障等。下面将详细分析电源时序器跳闸的

时序逻辑电路故障分析

时序逻辑电路的主要故障分析是一个复杂而重要的课题,它涉及电路的稳定性、可靠性以及整体性能。以下是对时序逻辑电路主要故障的全面分析,旨在帮助理解和解决这些故障。

FPGA 高级设计:时序分析和收敛

Static Timing Analysis,简称 STA。它可以简单的定义为:设计者提出一些特定的时序要求(或者说是添加特定的时序约束),套用特定的时序模型,针对特定的电路进行

发表于 06-17 17:07

Xilinx FPGA编程技巧之常用时序约束详解

Register-to-Register Constraint

寄存器到寄存器约束往往指的是周期约束,周期约束的覆盖范围包括:

覆盖了时钟域的时序要求

覆盖了同步数据在内部寄存器

发表于 05-06 15:51

FPGA工程的时序约束实践案例

详细的原时钟时序、数据路径时序、目标时钟时序的各延迟数据如下图所示。值得注意的是数据路径信息,其中包括Tco延迟和布线延迟,各级累加之后得到总的延迟时间。

发表于 04-29 10:39

•812次阅读

时序约束实操

添加约束的目的是为了告诉FPGA你的设计指标及运行情况。在上面的生成约束之后,在Result àxx.sdc中提供约束参考(请注意该文件不能直接添加到工程中,需要热复制到别的指定目录或者新建自己的SDC文件添加到工程)。

Xilinx FPGA编程技巧之常用时序约束详解

寄存器到寄存器约束往往指的是周期约束,周期约束的覆盖范围包括:

覆盖了时钟域的时序要求

覆盖了同步数据在内部寄存器之间的传输

分析一个单独

发表于 04-12 17:39

6SE70 1200KW变频器平衡电阻爆炸的原因?

损坏,V相下半桥两个阻容吸收板电容脚融焊,W相叠层母排绝缘层损坏,使用前测得进线电压为603V,在新疆使用,各位大神帮忙分析下可能产生这种现象的原因,谢谢~~

发表于 01-10 08:22

时序约束爆炸的原因研究分析

时序约束爆炸的原因研究分析

评论