- Load:0 second

- Duration:0 second

- Size:0x0

- Volume:0%

- Fps:60fps

- Sudio decoded:0 Byte

- Video decoded:0 Byte

MicroBlaze 是基于Xilinx公司FPGA的微处理器IP核,和其它外设IP核一起,可以完成可编程系统芯片(SOPC)的设计。MicroBlaze 处理器采用RISC架构和哈佛结构的32位指令和数据总线,可以全速执行存储在片上存储器和外部存储器中的程序,并访问其的数据。

通过视频了解如何在IP Integrator中创建简单的MicroBlaze设计,并创建一个在KC705目标板上运行的简单软件应用程序。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

芯片

+关注

关注

458文章

51386浏览量

428411 -

赛灵思

+关注

关注

32文章

1794浏览量

131576 -

微处理器

+关注

关注

11文章

2275浏览量

82864

发布评论请先 登录

相关推荐

如何理解芯片设计中的IP

本文主要介绍如何理解芯片设计中的IP 在芯片设计中,IP(知识产权核心,Intellectual Property Core)是指在芯片设计中

如何在Linux系统上设置站群服务器IP地址

在Linux系统上设置站群服务器的IP地址,可以通过以下步骤进行,主机推荐小编为您整理发布如何在Linux系统上设置站群服务器IP地址。

如何在TMS320C6727 DSP上创建基于延迟的音频效果

电子发烧友网站提供《如何在TMS320C6727 DSP上创建基于延迟的音频效果.pdf》资料免费下载

发表于 10-16 10:35

•0次下载

MicroBlaze V软核处理器的功能特性

本指南提供了有关 AMD Vivado Design Suite 中包含的 32 位和 64 位 MicroBlaze V 软核处理器的信息。该文档旨在用作为处理器硬件架构的指南,随附《RISC-V 指令集手册》第一卷和第二卷。

TCP IP协议属性设置中的IP配置

在现代网络中,TCP/IP协议是基础架构的重要组成部分。掌握TCP/IP协议属性设置中的IP配置对于确保网络的稳定性、性能和安全至关重要。本

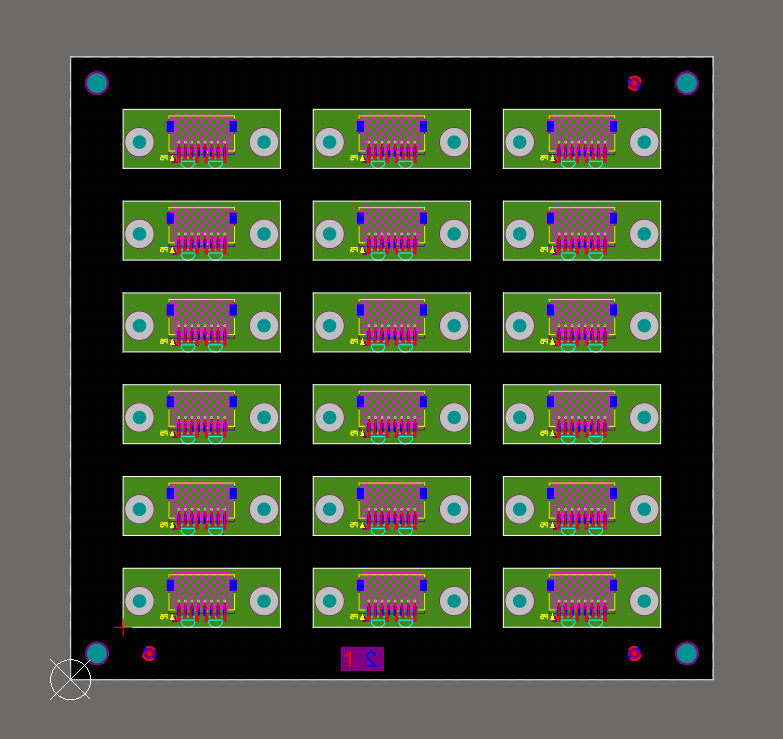

如何在Draftsman中创建PCB制造图纸

在制作PCB的过程中,绘制面板制造图纸是不可或缺的一步。单个PCB的制造图纸只显示单个PCB的钻孔和板特征,但这些需要合并到整个面板的一张图纸中。根据不同公司或制造商的具体需求,一些设计团队需要接手创建面板图纸,包括指定拆板方法

如何在引脚映射器文件中添加TC322?

我想在AURIX Development Studio中为 TC322 创建一个引脚映射文档。

遗憾的是,我只能在那里找到 TC33X 及更高版本。

如何在这里添加所需的控制器?

发表于 07-04 07:01

AMD FPGA中MicroBlaze的固化流程详解

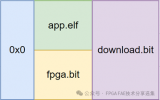

AMD FPGA在配置了适当的启动模式后,上电即会按该模式去加载配置文件。以7系列FPGA为例,假设设置模式引脚M[2:0]=3’b001,上电后FPGA会以Master SPI方式尝试从FLASH加载配置文件,其与工程是否含有MicroBlaze IP无关。

发表于 04-25 12:49

•645次阅读

如何利用Tcl脚本在Manage IP方式下实现对IP的高效管理

在Vivado下,有两种方式管理IP。一种是创建FPGA工程之后,在当前工程中选中IP Catalog,生成所需IP,这时相应的IP会被自动

利用ISE与Matlab创建并仿真FPGA设计中的ROM IP核

一般都是先创建MIF文件,将图像中的像素信息用一个ROM储存起来,然后调用ROM里面的地址进行处理,相当于制作了一个ROM查找表。

发表于 04-16 11:49

•728次阅读

如何在IP Integrator中创建MicroBlaze设计

如何在IP Integrator中创建MicroBlaze设计

评论