声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

asic

+关注

关注

34文章

1206浏览量

120678 -

赛灵思

+关注

关注

32文章

1794浏览量

131453 -

时钟

+关注

关注

11文章

1746浏览量

131713

发布评论请先 登录

相关推荐

CPLD 与 ASIC 的比较

在数字电子领域,CPLD和ASIC是两种广泛使用的集成电路技术。它们各自有着独特的优势和局限性,适用于不同的应用场景。 1. 定义与基本原理 1.1 CPLD(复杂可编程逻辑器件) CPLD是一种

微服务容器化部署好处多吗?

微服务容器化部署好处有很多,包括环境一致性、资源高效利用、快速部署与启动、隔离性与安全性、版本控制与回滚以及持续集成与持续部署。这些优势助力应用可靠稳定运行,提升开发运维效率,是现代软件架构的优质选择。UU云小编认为微服务容器化部署好处

ASIC和GPU的原理和优势

本文介绍了ASIC和GPU两种能够用于AI计算的半导体芯片各自的原理和优势。 ASIC和GPU是什么 ASIC和GPU,都是用于计算功能的半导体芯片。因为都可以用于AI计算,所以也被称为“AI

Verilog 与 ASIC 设计的关系 Verilog 代码优化技巧

Verilog与ASIC设计的关系 Verilog作为一种硬件描述语言(HDL),在ASIC设计中扮演着至关重要的角色。ASIC(Application Specific Integrated

时序约束一主时钟与生成时钟

的输出,对于Ultrascale和Ultrascale+系列的器件,定时器会自动地接入到GT的输出。 1.2 约束设置格式 主时钟约束使用命令create_clock进行创建,进入Timing

ASIC集成电路如何提高系统效率

在现代电子系统中,效率和性能是衡量一个系统优劣的关键指标。随着技术的发展,ASIC集成电路因其高度定制化和优化的特性,在提高系统效率方面发挥着越来越重要的作用。 ASIC的定义和特点 ASIC是一种

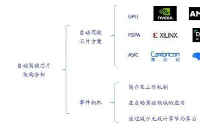

自动驾驶三大主流芯片架构分析

当前主流的AI芯片主要分为三类,GPU、FPGA、ASIC。GPU、FPGA均是前期较为成熟的芯片架构,属于通用型芯片。ASIC属于为AI特定场景定制的芯片。行业内已经确认CPU不适用于AI计算

恩智浦MCU解读 MCX A系列微处理器之时钟架构

全新的MCX A系列融合了恩智浦通用MCU的特点,适用更为广泛的通用应用,实现了低成本,低功耗,高安全性和高可靠性。 今天,大家一起来了解一下MCX A最新产品的时钟架构: MCXA153是MCX

发表于 06-20 09:21

•704次阅读

PSoC63在CM0和CM4之间拆分BLE堆栈有什么好处?

在 PSoC63 中,在 CM0 和 CM4 之间拆分 BLE 堆栈有什么好处?

设计具有多个EVAL_PASCO2_SENSOR和 BLE 6EDL_SPI_LINK的系统时,最佳实践(或架构)是什么?

发表于 05-17 08:46

FPGA和ASIC两者的设计流程

ASIC中你可以直接加宽金属线,比如两倍宽度走时钟线,复位线啦,之类的。金属线宽度变大,线上的延迟变小,对速度也是有帮助的。

发表于 03-19 13:53

•970次阅读

AMD推出全新Spartan UltraScale+ FPGA系列

AMD 已经拥有 Zynq UltraScale+ 和 Artix UltraScale+ 系列,而 Spartan UltraScale+ FPGA 系列的推出使其不断现代化。

发表于 03-18 10:40

•439次阅读

UltraScale系列与7系列FPGA的差异

已从该架构中移除BUFMRs、BUFRs、BUFIOs及其相关的路由资源,并被新的时钟缓冲器、时钟路由和全新的I/O时钟架构所取代。

PTP时钟源设备全攻略:从普通时钟到透明时钟的进阶之路

在现代通信技术中,精确时间同步对于保障网络性能至关重要。PTP(PrecisionTimeProtocol)时钟源设备作为实现高精度时间同步的关键组件,其配置和选择对于网络架构师和工程师来说至关重要

单板上时钟的注意事项 单板上时钟晶体下面铺地的好处

单板上时钟的注意事项 单板上时钟晶体下面铺地的好处 单板上时钟是指将时钟晶体组件直接铺装在电路板上,这种设计方案在电子设备中广泛应用。在介绍

新UltraScale ASIC时钟架构的使用及好处

新UltraScale ASIC时钟架构的使用及好处

评论