了解Vivado实现中2015.3中的新增量编译功能,包括更好地处理物理优化和自动增量编译流程。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

赛灵思

+关注

关注

32文章

1794浏览量

131246 -

编译

+关注

关注

0文章

657浏览量

32852 -

Vivado

+关注

关注

19文章

812浏览量

66470

发布评论请先 登录

相关推荐

SOLIDWORKS 2025设计新增功能

SOLIDWORKS 2025的发布为设计领域注入了新的活力,其新增功能不仅提升了设计效率,还增强了协作和数据管理的能力

ChatGPT新增实时搜索与高级语音功能

在OpenAI的第八天技术分享直播中,ChatGPT的搜索功能迎来了重大更新。此次更新不仅丰富了ChatGPT的功能体系,更提升了其实用性和竞争力。 新增的实时搜索

Vivado之实现布局布线流程介绍

一、前言 本文将介绍Vivado进行综合,以及布局布线的内部流程,熟悉该流程后结合Settings中对应的配置选项,对于时序收敛调试将更具有针对性。 二、Implementation(实现) 实现

SOLIDWORKS 2025新增功能介绍

在工程设计领域,SOLIDWORKS一直是创新的代名词,其不断推出的新版本总能带给用户惊喜。2025年的SOLIDWORKS再次不负众望,带来了一系列令人瞩目的新增功能,旨在提升设计效率、增强用户体验,并推动工程设计的边界。

HyperLynx 2409的新增部分功能

在《HyperLynx 2409丨新一代电子系统设计的革新之旅(上)》中,我们介绍了HyperLynx 2409的新增部分。接下来,我们将继续深入探讨这些新功能如何帮助设计人员更有效地

每次Vivado编译的结果都一样吗

很多FPGA工程师都有这种困惑,Vivado每次编译的结果都一样吗? 在AMD官网上,有这样一个帖子: Are Vivado results repeatable for identical

HyperLynx 2409新增功能和改进功能

作为HyperLynx Schematic Analysis加入HyperLynx系列;Xpedition AMS即将作为HyperLynx AMS加入HyperLynx系列。我们的产品一如既往地出色,并具有以下新增功能和改进功能

使用Vivado通过AXI Quad SPI实现XIP功能

本博客提供了基于2023.2 Vivado的参考工程,展示如何使用Microblaze 地执行(XIP)程序,并提供一个简单的bootloader。

浅谈Vivado编译时间

随着FPGA规模的增大,设计复杂度的增加,Vivado编译时间成为一个不可回避的话题。尤其是一些基于SSI芯片的设计,如VU9P/VU13P/VU19P等,布局布线时间更是显著增加。当然,对于一些设计而言,十几个小时是合理的。但我们依然试图分析设计存在的问题以期缩短

AMD Vivado Design Suite 2024.1全新推出

AMD Vivado Design Suite 2024.1 可立即下载。最新版本支持全新 AMD MicroBlaze V 软核处理器,并针对 QoR 和 Dynamic Function

VSCODE ESP-IDF插件新增.c文件不会被编译是怎么回事?

VSCODE ESP-IDF插件新增.c文件不会被编译,需要clean后完整编译才会认得到。这样太费时间了

有没有办法直接编译这个新增的c文

发表于 06-07 06:57

Vivado编译常见错误与关键警告梳理与解析

Xilinx Vivado开发环境编译HDL时,对时钟信号设置了编译规则,如果时钟由于硬件设计原因分配到了普通IO上,而非_SRCC或者_MRCC专用时钟管脚上时,编译器就会提示错误。

如何禁止vivado自动生成 bufg

在Vivado中禁止自动生成BUFG(Buffered Clock Gate)可以通过以下步骤实现。 首先,让我们简要了解一下什么是BUFG。BUFG是一个时钟缓冲器,用于缓冲输入时钟信号,使其更稳

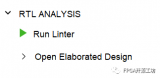

Vivado 2015.3中的新增量编译功能介绍

Vivado 2015.3中的新增量编译功能介绍

评论