声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

赛灵思

+关注

关注

32文章

1794浏览量

131733 -

design

+关注

关注

0文章

159浏览量

45936 -

Vivado

+关注

关注

19文章

819浏览量

67255

发布评论请先 登录

相关推荐

AXI 接口设计避坑指南:AXI接口笔记

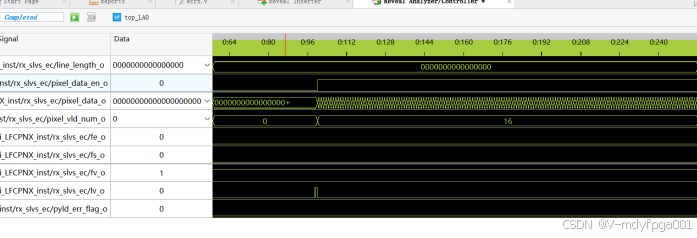

AXI接口笔记 第一章 问题记录 第1节 接收数据全0或全1 1.1 问题现象 上图中,pixel_data_o是EC IP核输出的图像数据,正确的话会如上图所示,图像数据每个时钟会变化并且值

Vivado FIR IP核实现

Xilinx的FIR IP核属于收费IP,但是不需要像 Quartus那样通过修改license文件来破解。如果是个人学习,现在网络上流传的license破解文件在破解Vivado的同时也破解

Vivado Design Suite用户指南: 设计分析与收敛技巧

电子发烧友网站提供《Vivado Design Suite用户指南: 设计分析与收敛技巧.pdf》资料免费下载

发表于 01-15 15:28

•0次下载

Vivado Design Suite用户指南:逻辑仿真

电子发烧友网站提供《Vivado Design Suite用户指南:逻辑仿真.pdf》资料免费下载

发表于 01-15 15:25

•0次下载

AMD Vivado Design Suite 2024.2全新推出

AMD Vivado Design Suite 2024.2 全新推出,使用 AMD Versal Adaptive SoC 进行设计的重大改进。此版本为 AMD Versal 自适应 SoC

U50的AMD Vivado Design Tool flow设置

AMD Alveo 加速卡使用有两种流程,AMD Vitis Software Platform flow 和 AMD Vivado Design Tool flow。比较常见的是 Vitis

vivado导入旧版本的项目,IP核心被锁。

vivado导入其他版本的项目的时候,IP核被锁,无法解开,请问该如何解决。

使用软件:vivado 2019.2

导入项目使用版本:vivado 2018

发表于 11-08 21:29

使用Vivado通过AXI Quad SPI实现XIP功能

本博客提供了基于2023.2 Vivado的参考工程,展示如何使用Microblaze 地执行(XIP)程序,并提供一个简单的bootloader。

AMD Vivado Design Suite 2024.1全新推出

AMD Vivado Design Suite 2024.1 可立即下载。最新版本支持全新 AMD MicroBlaze V 软核处理器,并针对 QoR 和 Dynamic Function

Xilinx NVMe AXI4主机控制器,AXI4接口高性能版本介绍

NVMe AXI4 Host Controller IP可以连接高速存储PCIe SSD,无需CPU,自动加速处理所有的NVMe协议命令,具备独立的数据写入和读取AXI4接口,不但适用

浅谈Pango_Design_Suite工具的安装

要不要安装并口驱动,为了兼容性更好,笔者这里选择安装,而后即完成并口的外设接口的驱动安装。

至此,Pango_Design_Suite工具安装全部完成,然后我们可以直接打开Pango Design

发表于 05-30 00:43

如何使用Vivado Design Suite IP Integrator的调试AXI接口

如何使用Vivado Design Suite IP Integrator的调试AXI接口

评论