Kintex®-7 FPGA KC705 评估套件包括硬件、设计工具、IP 核和预验证参考设计等的所有基本组件,参考设计中包含能实现高性能、串行连接功能和高级存储器接口的目标设计。随套件提供预验证参考设计和行业标准 FPGA 夹层连接器(FMC),能够利用子卡实现升级和定制。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

存储器

+关注

关注

38文章

7448浏览量

163589 -

赛灵思

+关注

关注

32文章

1794浏览量

131159 -

IP

+关注

关注

5文章

1643浏览量

149323

发布评论请先 登录

相关推荐

ADC12DL3200EVM评估板lvds接口是标准的FMC接口吗?

我查看原理图首页框图标注FMC,但引脚定义似乎与普通fmc不同:

第一图为ADC12DL3200EVM,A1 A2是一对差分对,图2是Xilinx KC705的fmc接口,A2 A3是一对,是否代表不能兼容

发表于 11-22 06:45

AMD/Xilinx Zynq® UltraScale+ ™ MPSoC ZCU102 评估套件

AMD/Xilinx Zynq® UltraScale+ ™ MPSoC ZCU102 评估套件可快速启动汽车、工业、视频和通信应用设计。AMD/Xilinx MPSoC ZCU102

想要与ADC32J25EVM和TSW14J50EVM完成一个完整的闭环测试,应当如何设置发射端?

,我的发射端使用的是DAC38RF82EVM以及TSW14J10EVM、KC705,若想要与ADC32J25EVM和TSW14J50EVM完成一个完整的闭环测试,应当如何设置发射端?

希望能够得到一个完整的操作流程步骤,感谢!

发表于 11-15 07:05

如何在服务器上调试本地FPGA板卡

到本地板卡的 FPGA。之后的调试不需要重复连接。

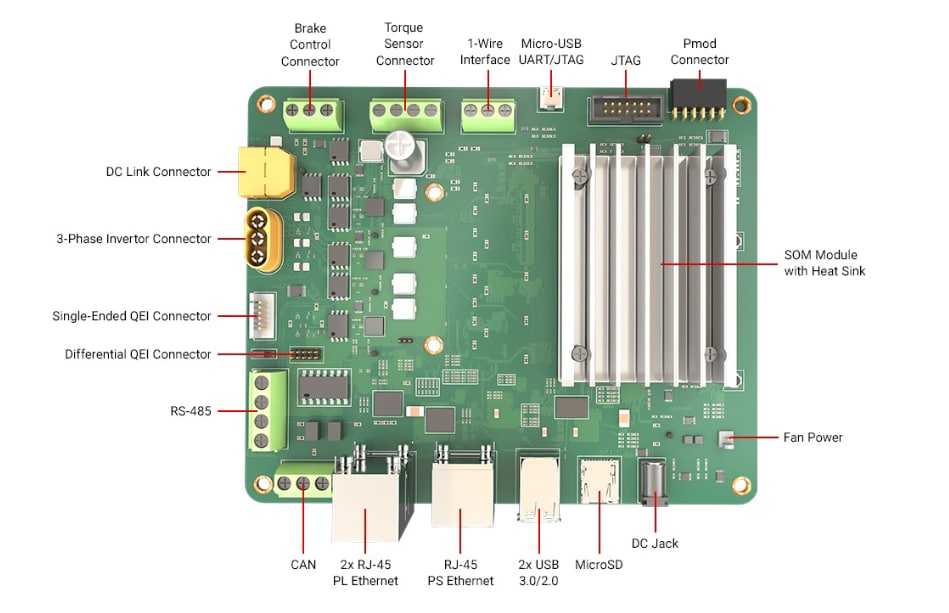

本教程使用 Xilinx Kintex-7 FPGA KC705 评估套件,如图 1 所示。

图一

发表于 07-31 17:36

求一块XILINX开发板KC705,VC707,KC105和KCU1500

你好,求购一块XILINX开发板KC705,VC707,KC105和KCU1500,要求原厂正品功能正常,全新和2手(无拆修)都行,哪位工程师闲置了可以联系我,谢谢。

企鹅:299零57零314

发表于 07-20 00:34

TRACO Power AC/DC工业电源产品特性

本期DigiKeyDaily 向大家推荐两款产品——TRACO Power TPI 50A-J系列AC/DC工业电源和AMD Xilinx Kria KR260机器人入门套件。

使用JESD204B连接AD9164时,CGS过程无法完成是什么原因导致?

我使用的是KC705板卡,调用了里面JESD204B的IP核,使用模式为interpolation值为4,4条链路,DAC频率为2.5GHZ,通道速度为6.25GHZ,出现的问题是:

帧同步过程

发表于 12-12 07:28

AD9467输出电平标准为LVDS,是否支持连接FPGA BANK1.8V?

我已经看过AD9467的评估板在ZEDboard和KC705的引脚约束为\"LVDS_25\",对应FPGA的BANK VCCO供电2.5V,但是现在我的项目中FPGA BANK 的VCCO供电是1.8V,我对其做引脚约束为\"LDVS\"可行吗?

发表于 12-11 06:36

使用KC705板上晶振作为参考时钟生成DCI和data,有很多跳动的杂波信号是怎么回事?

最近配置AD9139的时候,分别采用了两种方式。一种是直接使用KC705板上晶振作为参考时钟生成DCI和data,DAC单独供参考时钟,另一种是使用AD9139评估板分频得到的DCO作为FPGA

发表于 12-04 06:53

Xilinx Power Advantage采用KC705评估套件演示

Xilinx Power Advantage采用KC705评估套件演示

评论