本视频介绍了7系列CLB架构,包括:LUT,触发器,专用多路复用器,进位链和其他资源。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1664文章

22508浏览量

639431 -

赛灵思

+关注

关注

33文章

1798浏览量

133671 -

触发器

+关注

关注

14文章

2065浏览量

63568

发布评论请先 登录

相关推荐

热点推荐

赛灵思FPGA电源解决方案全解析

个复杂且关键的环节。本文将深入探讨赛灵思(Xilinx)FPGA的电源解决方案,为电子工程师们提供全面的参考。 文件下载: MAX17017DEVKIT+.pdf FPGA概述 FPGA是一种可编程设备,由通过可编程互连连接的可

Altera Agilex FPGA与SoC实现更智能的AI

在本期专题中,Altera 院士兼首席架构师 Ilya Ganusov 将带大家深入解析 Altera FPGA 创新的三大核心支柱:性能、AI 加速与安全,同时拆解 Agilex 7 FPG

Azukar-FPGA开源FPGA教育开发板介绍

初学 FPGA 数字设计总遇坎?商用开发板绑定专有工具链,学习成果无法跨项目复用;元件封装稀有难焊接,新手手动装配频频失败;设计文件不公开,想复刻改造却无据可依;开发板架构固定,适配不了实验室多样的实训需求?

XC7Z020-2CLG484I 双核异构架构 全能型 SoC

Zynq-7000 系列的核心型号,创新性地将双核 ARM Cortex-A9 处理器与 7 系列 FPGA 可编程逻辑深度集成,构建起 “软件可编程 + 硬件可定制” 的异构计算

发表于 02-28 23:37

核芯互联正式发布国产高性能时钟缓冲器芯片CLB7043

近日,核芯互联正式发布了面向高端通信与数据转换系统的国产高性能时钟缓冲器芯片——CLB7043。作为一款集成了时钟分发、相位管理、确定性同步等复杂功能的高性能模拟芯片,CLB7043在核心的相位噪声

AMD UltraScale架构:高性能FPGA与SoC的技术剖析

™ FPGA.pdf 架构概述 UltraScale架构涵盖了高性能FPGA、MPSoC和RFSoC等多个产品系列,旨在通过创新技术满足广泛

基于DSP与FPGA异构架构的高性能伺服控制系统设计

DSP+FPGA架构在伺服控制模块中的应用,成功解决了高性能伺服系统对实时性、精度和复杂度的多重需求。通过合理的功能划分,DSP专注于复杂算法和上层控制,FPGA处理高速硬件任务,两者协同实现了传统

使用Xilinx 7系列FPGA的四位乘法器设计

(Shinshu University)研究团队的最新设计中,一个专为 Xilinx 7 系列 FPGA 量身打造的 4 位乘法器使用了仅 11 个 LUT + 2 个 CARRY4 块,关键路径延迟达到 2.75 ns。这是一

【VPX650 】青翼凌云科技基于 VPX 系统架构的 VU13P FPGA+ZYNQ SOC 超宽带信号处理平台

VPX650 是一款基于 6U VPX 系统架构的 VU13P FPGA + XC7Z100 SOC 超宽带信号处理平台,该平台采用一片 Xilinx 的 Virtex UltraScale+

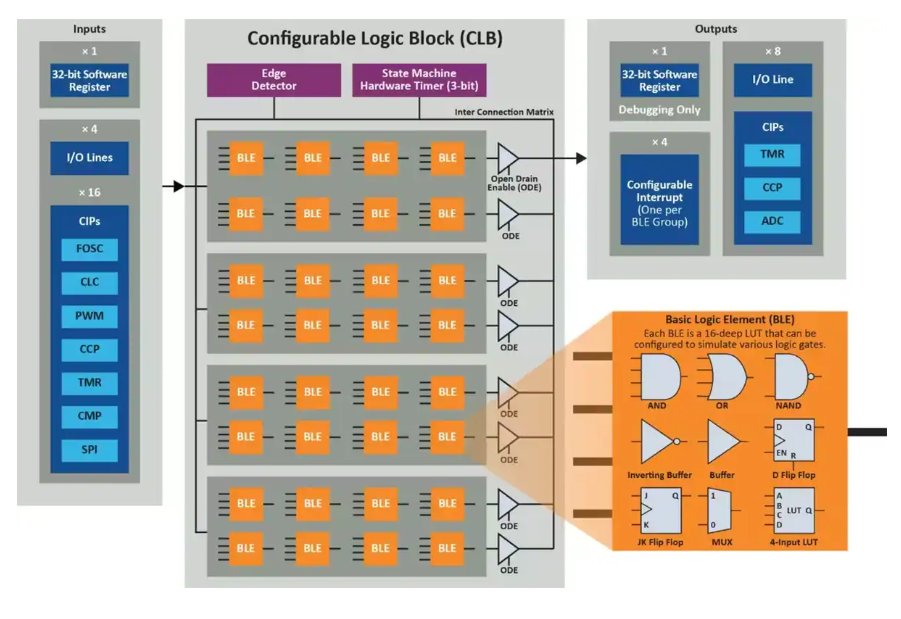

PIC16F13145微控制器技术解析:CLB架构与低功耗设计

PIC16F13145微控制器采用可配置逻辑块(CLB),其中包含32个独立逻辑单元,并带有可自定义的查找表(LUT),用于基于硬件的自定义逻辑。 如此可以实现独立于CPU的运行,从而缩短响应时间并降低功耗。此系列

【TES600G】青翼凌云科技基于JFM7K325T FPGA+FT-M6678 DSP的全国产化信号处理平台

的Kintex-7系列FPGAJFM7K325T16作为协处理单元,具有1个FMC子卡接口,具有4路SFP+万兆光纤接口,具有2路RJ45千兆以太网接口,其中1路挂在FP

一文详解xilinx 7系列FPGA配置技巧

本文旨在通过讲解不同模式的原理图连接方式,进而配置用到引脚的含义(手册上相关引脚含义有四、五页,通过本文理解基本上能够记住所有引脚含义以及使用场景),熟悉xilinx 7系列配置流程,以及设计原理图时需要注意的一些事项,比如flash与

Altera Agilex 3 FPGA和SoC产品介绍

Altera 的 Agilex 3 FPGA 和 SoC 可在不影响性能的前提下显著提高成本效益。其通过出色的 Hyperflex FPGA 架构、先进的收发器技术、更高的集成度和更强大的安全

Xinlinx 7系列FPGA的CLB架构介绍

Xinlinx 7系列FPGA的CLB架构介绍

评论