从视频中了解异常约束的不同类型,并详细查看错误路径、min/max 延迟和案例分析约束。我们还将检查异常优先级和技巧,以限制异常约束。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

视频

+关注

关注

6文章

1960浏览量

73211 -

赛灵思

+关注

关注

32文章

1794浏览量

131579 -

优先

+关注

关注

0文章

3浏览量

6819

发布评论请先 登录

相关推荐

用MSP430g2553对LDC1000操作,在程序里却不能设置LDC1000的Rp-MAX和Rp-MIN的值,为什么?

用MSP430g2553对LDC1000操作,是在程序里却不能设置LDC1000的Rp-MAX和Rp-MIN的值.不论设置什么值.程序读出的l两值都为:Rp-MAX=0x14,Rp-MIN

发表于 01-17 08:35

用MSP430F8828和LDC1000制成了一块应用板,在程序里却不能设置LDC1000的Rp-MAX和Rp-MIN的值,为什么?

里却不能设置LDC1000的Rp-MAX和Rp-MIN的值.不论设置什么值.

程序读出的l两值都为:Rp-MAX=0x13,Rp-MIN=0x3D.这就使LDC1000不能完成正常转换

发表于 01-06 06:23

socket编程中的错误处理技巧

Socket编程是网络编程的基础,它允许程序之间通过TCP/IP协议进行通信。然而,网络通信是不稳定的,可能会遇到各种问题,如网络延迟、连接中断、数据丢失等。 错误处理的重要性 提高程序的健壮性

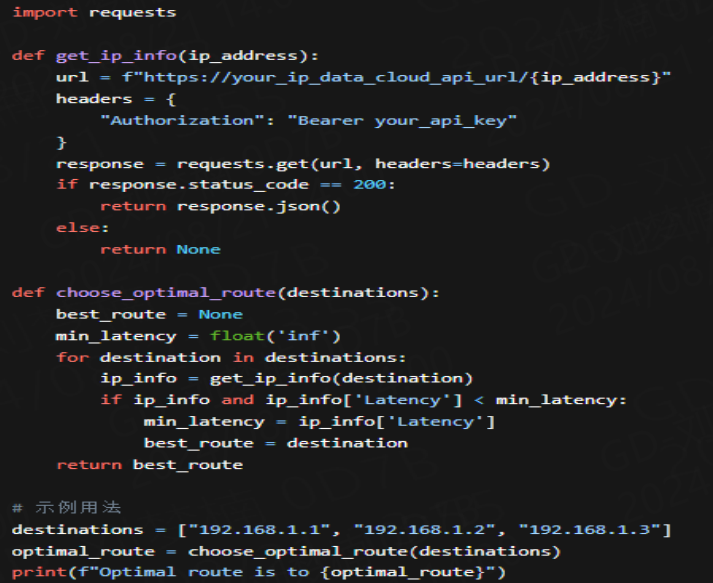

SD-WAN技术在直播网络中如何实现智能路径选择?

SD-WAN技术在直播网络中实现智能路径选择主要通过以下几个步骤: 1、实时网络监控:SD-WAN系统持续监控所有可用的网络路径,包括它们的带宽、延迟、丢包率和抖动等关键性能指标。 2、路径

路由偏好,提升网络性能新路径

网络设备在选择路由路径时所倾向的特定策略或条件。它基于多种因素进行决策,例如网络延迟、带宽、可靠性、成本等。可分为以下几类: 1.基于性能的路由偏好:以网络延迟和带宽等性能为指标,力求实现快速数据传输。比如实时视频会议等

RTOS SDK 1.4.0 espconn_tcp_set_max_con_allow导致代码崩溃了怎么解决?

;conn, onNewClient);

espconn_accept(&conn);

espconn_tcp_set_max_con_allow(&conn, 2

发表于 07-18 06:57

浅谈半导体芯片失效分析Analysis of Semiconductor Chip Failure

共读好书 失效专业能力分类 元器件5A试验介绍(中英文) ◆PFA (Physical Feature Analysis) 物理特征分析 ◆DPA (Destructive Physical

使用ESP8266模块进行UDP传输,重新连接路由后发送数据有延迟怎么避免?

);wifi_station_set_reconnect_policy(1),设置成自动连接路由,UDP每1S发送一条数据(100字节),如果正在正常发送数据的时候路由器断电,UDP服务器收不到数据,路由再上电后,从模块WIFI GOT IP到UDP服务器再次收到数据有差不多一分钟的

发表于 07-12 06:06

ESP32-WROOM esp-idf4.4-dev使能自动浅睡眠串口打印部分乱码怎么解决?

_freq_mhz = CONFIG_EXAMPLE_MAX_CPU_FREQ_MHZ, /* 最大CPU时钟频率 */ .min_freq_mhz = CONFIG_EXAMPLE_MIN_CPU_FREQ_MHZ, /* 没

发表于 06-20 07:52

在不同的电脑上启动同一套代码时,出现编译路径错误的提示怎么解决?

不同的电脑上安装esp-idf的路径不同时,启动同一套代码时会出现:

无法找到“D:\\Espressif\\tools\\xtensa-esp32-elf\\esp-2022r1-11.2.0

发表于 06-11 06:54

第7行if(sys_ctrl.find==0) 编译出现02.c(7): error C200: left side of \'.\'

,3,0);

//时间调节位置闪烁

switch(sys_ctrl.set_time_mode)

{

case 1://时

lcd1602_show_string(6,0,\"

发表于 05-08 20:06

STM32F030R8电机驱动函数中电机位置数值跳变的原因?

,int mode)

{

int xc_max,xc_min;

switch(motor0_x)

{

case 0:

{

xc_max=m0_xc_

发表于 04-30 06:21

【米尔-芯驰D9360商显板试用评测】3、LED闪起来

_height = QString(\"min-height: %1px;\").arg(size);// 最小高度:size

QString max_width = QString(\"

发表于 04-02 18:00

NCP1015反激开关电源multisim仿真错误

=======

Warning: Analysis initial conditions are not set to User-Defined, but initial conditions are set

发表于 03-22 23:03

请问如何在CX3中保存已更改的属性值?

);

break;

case CX3_USB_UVC_GET_MIN_REQ: // Minimum gammaVal = 26.

glGammaEp0Buffer[0] = 26

发表于 03-06 08:33

错误路径、 Min-Max延迟和Set_Case_Analysis

错误路径、 Min-Max延迟和Set_Case_Analysis

评论